*18èmes Journées Pédagogiques*

**CCMO**

*Saint-Malo*

3–5 décembre 2025

# Dix-huitièmes journées Pédagogiques JPCNFM2025

Centre Commun de Microélectronique de l'Ouest

Saint Malo 3 - 5 décembre 2025

Palais du Grand Large

Organisées par

Avec le soutien de :

Édité par : Olivier Bonnaud, Laurent Pichon, Anne-Claire Salaün, Hervé Lhermite

---

© 2025 Université de Rennes I

Centre Commun de Microélectronique de l'Ouest

ISBN 978-2-9522395-0-9

## EDITORIAL des Actes des JPCNFM'2025

L. Pichon<sup>a</sup>, AC. Salaün<sup>a</sup>, H. Lhermite<sup>a</sup>, O. Bonnaud<sup>a,b</sup>

<sup>a</sup> IETR et pôle CNFM de Rennes (CCMO), Université de Rennes, Rennes, France

<sup>b</sup> GIP-CNFM, Grenoble, France

Contacts email : olivier.bonnaud@univ-rennes.fr, lorraine.chagoya@grenoble-inp.fr

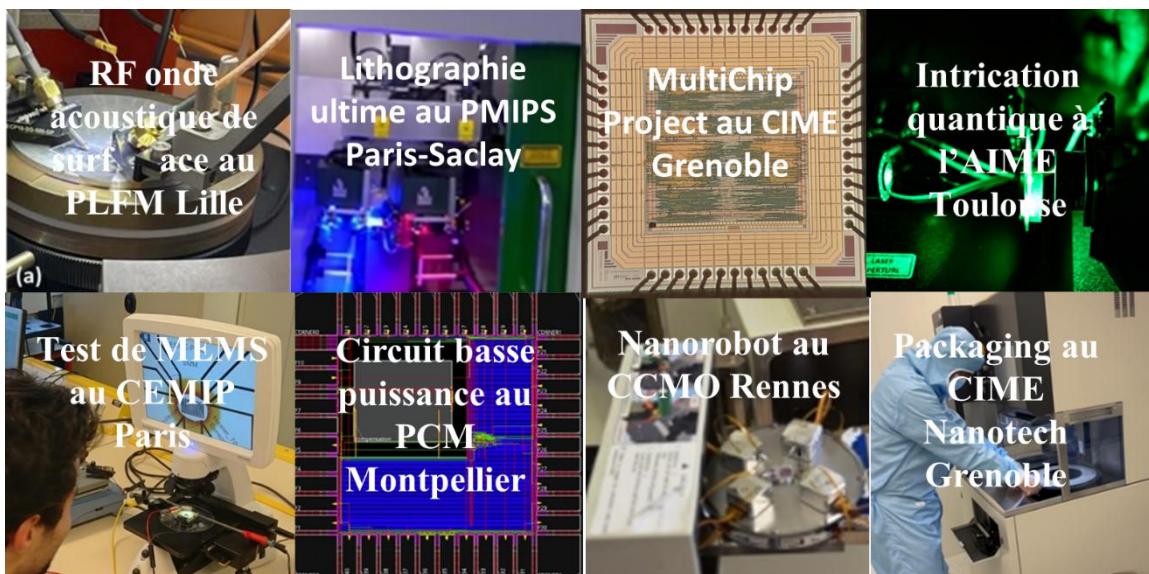

Depuis 1990, les Journées Pédagogiques de la Coordination Nationale pour la Formation à la Microélectronique et aux Nanotechnologies (JPCNFM) sont un moment important pour le GIP-CNFM (1) et toute sa communauté. Après une 17ème édition organisée à Toulouse par nos collègues de l'AIME en 2023, c'est de nouveau à Saint-Malo que ces Journées sont organisées en 2025.

Dans un contexte de Plan de Relance France 2030, plus particulièrement dans le domaine de l'électronique, et de positionnement du réseau au sein de la Filière électronique avec notre premier partenaire industriel ACSIEL Alliance électronique (2), l'objectif de ces 18èmes Journées Pédagogiques du CNFM garde le même esprit que les éditions précédentes (3). Il s'agit d'encourager, d'une part les échanges à caractère pédagogique entre enseignants et partenaires industriels de notre communauté afin de faire évoluer les contenus, et d'autre part, l'apprentissage au savoir-faire dans les nouvelles priorités industrielles, de recherche et de formation. Ces priorités, mises en évidence dans le cadre de la Filière électronique, concernent les défis associés à la réduction de la consommation d'énergie et des ressources naturelles, défis majeurs au niveau mondial.

L'approche de ces journées est d'autant plus importante dans le cadre de l'Appel à Manifestation d'Intérêt AMI-CMA, dont le projet sur 5 ans, intitulé INFORISM (4) piloté par le GIP-CNFM a été accepté. Il engage notre communauté académique ainsi que nos partenaires industriels. En effet, il s'agit d'une part de conserver la qualité de la formation de nos futurs diplômés en garantissant un savoir-faire adapté à l'industrie et la recherche en microélectronique, et d'autre part d'augmenter ce nombre de formés quels qu'en soient leurs origines et leur niveau de formation. Nous devons ainsi faire face à un défi important aussi bien technique et technologique qu'humain.

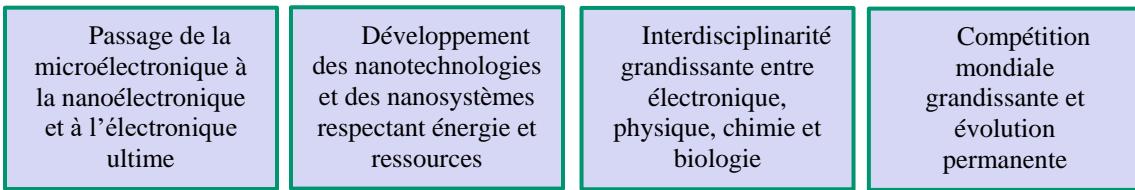

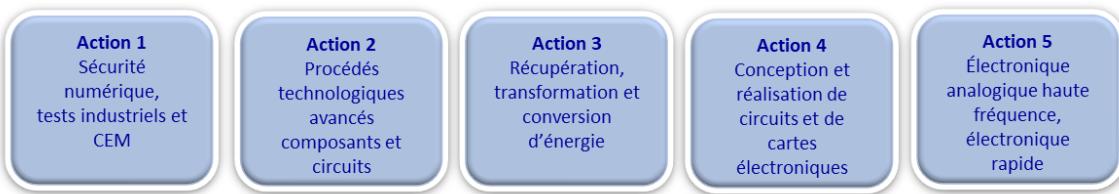

Les thématiques de ces journées concernent aussi bien la technologie, la conception, le test ou la caractérisation associés aux performances et aux innovations des circuits micro- et nanoélectroniques, VLSI, de puissance ou de grande surface, ou encore des circuits hybrides, hyperfréquences ou pour les télécommunications. Mais une attention particulière doit porter sur les nouveaux besoins en compétences manifestés par la profession au sein de la Filière Électronique et de son Comité Stratégique (5), afin de répondre aux différentes applications sociétales, mais aussi avec un objectif de réduction de la consommation énergétique de l'ensemble du domaine numérique et de couverture des métiers en tension. Il s'agit en particulier des systèmes toujours plus intelligents, connectés et sécurisés, des cartes électroniques, et de l'électronique de puissance, appliqués en priorité à la mobilité mais aussi à la conversion d'énergie électrique et à l'ensemble des applications sociétales. Lors de cette édition les différents acteurs du réseau présenteront les activités innovantes s'inscrivant dans les besoins de la filière et des objectifs du projet INFORISM. Une attention sera aussi portée au domaine de l'électronique quantique, dans lequel certains collègues sont déjà impliqués, qui est actuellement très soutenu par la recherche, et qui pourrait présenter des avantages à long terme quant à ses performances de sécurité et de

calcul. Ce domaine devrait contribuer à réduire la consommation d'énergie encore trop élevée dans la configuration actuelle.

Dans un contexte d'extension du numérique, notamment vers les supports pédagogiques en ligne, compléments indispensables à l'approche de l'apprentissage en ligne de plus en plus dominante, un effort doit être fourni vers le savoir-faire des techniciens, ingénieurs et docteurs. Le réseau et les pôles s'inscrivent dans cette approche innovante accrue aussi bien en formation initiale qu'en formation tout au long de la vie.

Sous la forme d'exposés ou de démonstrations de réalisations destinés à la dissémination au sein du réseau, les innovations pédagogiques ont été complétées par des expériences de sensibilisation de notre discipline vers les lycées et collèges, et également vers le grand public et les entreprises, dans le cadre de la politique d'attractivité du GIP-CNFM et du Comité Stratégique de Filière. Cette action s'inscrit dans l'objectif d'accroître le vivier de compétences quantitativement et qualitativement dans tous les volets de la microélectronique et de ses applications, et pour tous les niveaux de formations, de diplômes et de certifications, du brevet de technicien au doctorat en passant par le Bachelor, le Master ou l'ingénierat.

Le numéro spécial des J3eA associé à cette conférence doit compiler les principaux articles s'inscrivant dans la stratégie du réseau CNFM en bénéficiant de la possibilité d'une présentation en ligne, et donc agrémentée d'outils dynamiques. Il constitue une vitrine des activités du réseau CNFM, du consortium du projet ANR-11-IDFI-0017-FINMINA (6) qui s'est terminé en 2020 mais dont les apports en innovation de plateformes techniques sont toujours opérationnels, et par le consortium du projet ANR-23-CMAS-0024-INFORISM, qui a débuté à l'automne 2023.

Les organisateurs remercient tous les rédacteurs de leurs contributions qui devraient enrichir cet évènement bisannuel. Celui-ci devrait contribuer à disséminer des innovations pédagogiques, à accroître l'attractivité élargie du domaine et à renforcer les échanges et savoir-faire au sein de la communauté des scientifiques et des techniciens du domaine.

## Références

1. GIP-CNFM : Groupement d'Intérêt Public - Coordination Nationale pour la Formation en Microélectronique et en nanotechnologies. Website: <http://www.cnfm.fr>

2. ACSIEL Alliance Electronique. Website: <http://www.acsiel.fr/en-GB/index.aspx> (dernière consultation octobre 2025)

3. J3eA, Volume 21 Hors-série, 12 juillet 2024, JPCNFM 2023 – 17<sup>èmes</sup> journées pédagogiques du CNFM (Coordination Nationale pour la Formation en Micro-électronique et en nanotechnologies)

4. INFORISM, INGénierie de FORMations Innovantes et Stratégiques en Microélectronique, projet ANR-23-CMAS-0024-INFORISM au titre du programme France 2030

5. Comité Stratégique de Filière, CSF, <https://www.filiere-electronique.fr/>

6. FINMINA : Formation Innovante en Microélectronique et Nanotechnologie, projet ANR-11-IDFI-0017-FINMINA au titre du programme Investissement d'avenir

# **Dix-huitièmes Journées Pédagogiques**

## **Comité National d'Organisation**

|                         |          |              |                   |

|-------------------------|----------|--------------|-------------------|

| Jean-Luc Estienne       | ACSIEL   | ST Montrouge | Président         |

| Olivier Bonnaud         | GIP-CNFM | Grenoble     | Directeur Général |

| Marc Respaud            | AIME     | Toulouse     | Organisateur      |

| Laurent Pichon          | CCMO     | Rennes       |                   |

| Jean-Jacques Ganem      | CEMIP    | Paris Centre |                   |

| Ahmad Bsiesy            | CIME     | Grenoble     |                   |

| Bruno Allard            | CIMIRLY  | Lyon         |                   |

| Wilfried Uhring         | MIGREST  | Strasbourg   |                   |

| Philippe Pannier        | PACA     | Marseille    |                   |

| Jean Tomas              | PCB PCM  | Bordeaux     |                   |

| Pascal Benoit           | PLFM     | Montpellier  |                   |

| Virginie Hoël           | PLM      | Lille        |                   |

| Bruno Barelaud          | PLFM     | Limoges      |                   |

| Guillaume Agnus         | PMIPS    | Paris-Saclay |                   |

| Lorraine Chagoya-Garzon | GIP-CNFM | Grenoble     | Secrétariat       |

## **Comité Local d'organisation**

|                    |             |

|--------------------|-------------|

| Laurent Pichon     |             |

| Anne-Claire Salaün |             |

| Hervé Lhermite     | IETR Rennes |

| Fanny Le Boulch    |             |

| Fabienne Jégousse  |             |

## PROGRAMME JPCNFM'2025

### MERCREDI 3 DECEMBRE 2025

11 h 00 ACCUEIL

12 h 00 DÉJEUNER

#### *Conseil d'Orientation*

**13 h 30 Ouverture du Conseil d'Orientation et accueil des participants**

O1

Laurent Pichon, Anne-Claire Salaün et Hervé Lhermite (organisateurs des JPCNFM, pôle CCMO), David Alis (Président de l'Université de Rennes, sa représentante Anne-Claude Tarot Vice-Présidente Vie Etudiante), Jean-Luc Estienne (Président d'honneur du CNFM), Olivier Bonnaud (Directeur général du GIP-CNFM)

**13 h 45 Intervention du Président du GIP-CNFM**

O2

Jean-Luc Estienne (Président d'honneur du CNFM)

**14 h 00 GIP-CNFM : bilan 2021-2025, prorogation du réseau et perspectives**

O3

**dans le cadre du nouveau contrat 2026-2030 et bilan intermédiaire INFORISM**

Olivier Bonnaud (Directeur général du GIP-CNFM), Ahmad Bsiesy (Directeur adjoint du GIP-CNFM), Pascal Benoit (responsable services nationaux du GIP-CNFM)

**15 h 00 Information ACSIEL : évolution et enjeux**

O4

Sandrine Beaufils (Déléguée générale ACSIEL)

**15 h 15 Table ronde : Stratégie à moyen terme**

T1

Animation : Michel Robert (Professeur Polytech Montpellier, Université de Montpellier)

Panelistes :

Sylvie Retailleau (Professeur à l'Université Paris-Saclay et ancienne Ministre)

Hugues Metras (Directeur Agence des programmes ASIC, CEA)

Pascal Benoit (Responsable de la plateforme CAO)

Virginie Hoël (Représentante du GIP-CNFM au CSF)

Sandrine Beaufils (Déléguée générale ACSIEL)

Olivier Bonnaud (Directeur général du GIP-CNFM)

**16 h 30 PAUSE CAFE**

**17h00 Table ronde : coordination des AMI-CMA**

T2

Animation : Olivier Bonnaud (Directeur général du GIP-CNFM)

Panelistes :

Sylvie Retailleau (Professeur à l'Université Paris-Saclay et ancienne Ministre)

Maxime Pelcat (AMI-CMA ESOS, Rennes) en visio

Fabien Ndagijimana (AMI-CMA FAME, Grenoble)

Simon Hémour (AMI-CMA CAP ELENA, Bordeaux)

Jamal Rammal (AMI-CMA ESLAP, Redon)

Eve Langlet (IPR Académie de Rennes)

**18 h 00 FIN DU CONSEIL D'ORIENTATION**

**JEUDI 4 DECEMBRE 2025**

**LA FILIERE DANS UN CONTEXTE DE DEVELOPPEMENT

DURABLE ET RESPONSABILITE SOCIETALE**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <b>9 h 00</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Data centers : le revers énergétique du numérique</b>                                                                                                 | <b>O5</b>            |

| M. Robert<br><i>Université de Montpellier</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                          | <i>PCM</i>           |

| <b>9 h 30</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Fabrication de circuits intégrés durant des programmes doctoraux en technologie GaN et en 65nm : une accélération d'innovations</b>                   | <b>P1</b>            |

| <sup>1</sup> L. Trojman, <sup>2</sup> E. Holquin, <sup>2</sup> N. Pozo, <sup>1,2</sup> K. Vicuna, <sup>2</sup> L.-M. Procel, <sup>3</sup> F. Crupi, <sup>1</sup> F. Amiel<br><sup>1</sup> LISITE, Institut supérieur d'électronique de Paris, Issy-Les-Moulineaux<br><sup>2</sup> Université San Francisco de Quito (USFQ), Quito, Equateur<br><sup>3</sup> Université de Calabres, UNICAL, Rende, Italie                                                                                           |                                                                                                                                                          | <i>CEMIP</i>         |

| <b>9 h 35</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Une nouvelle approche de la stabilité des pérovskites pour une technologie photovoltaïque adaptée aux besoins énergétiques des objets numériques</b>  | <b>P2</b>            |

| <sup>1,2</sup> L.A Egbunu-David, <sup>1</sup> N. Doumit, <sup>2</sup> E. Ntsoenzok, <sup>1</sup> L. Trojman<br><sup>1</sup> LISITE, Institut supérieur d'électronique de Paris (Isip), 92130 Issy-les-Moulineaux<br><sup>2</sup> CEHMTI, Centre national de la recherche scientifique (CNRS), 45071, Orléans                                                                                                                                                                                        |                                                                                                                                                          | <i>CEMIP</i>         |

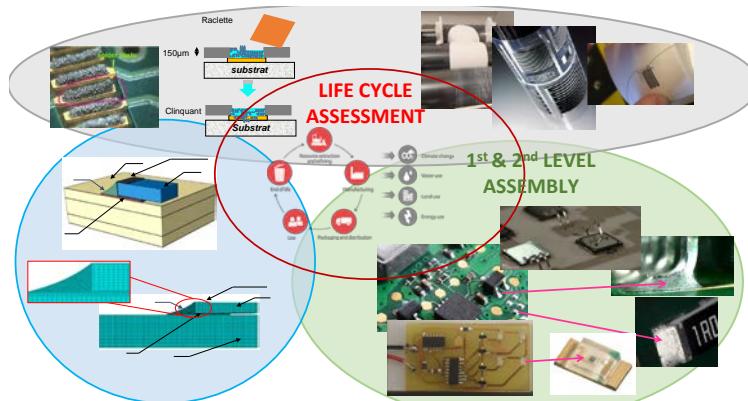

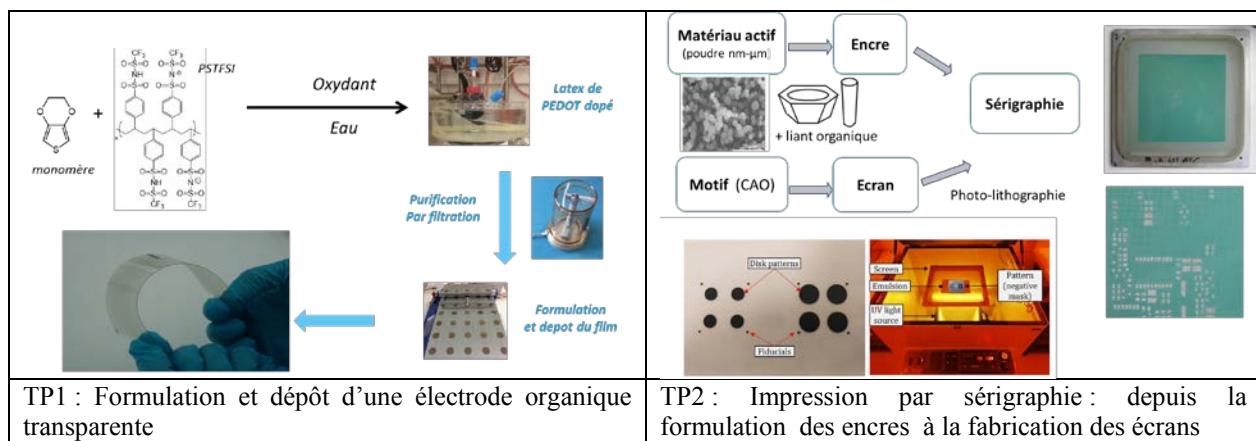

| <b>9 h 40</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Formation pluridisciplinaire autour de l'assemblage en microélectronique proposée à l'EDOC SPI de Bordeaux : un pas vers le développement durable</b> | <b>P3</b>            |

| <sup>1</sup> H. Debéda, <sup>1</sup> A. Gracia, <sup>2</sup> C. Brocho, <sup>2,3</sup> C. Bois, <sup>3,4</sup> N. Perry, <sup>1</sup> J. Tomas<br><sup>1</sup> Université de Bordeaux, Laboratoire IMS et pôle CNFM de Bordeaux (PCB), Talence<br><sup>2</sup> Université de Bordeaux, Laboratoire LCPO, Talence<br><sup>3</sup> Arts et Métiers Institute of Technology, CNRS, Bordeaux INP, Laboratoire I2M, Talence<br><sup>4</sup> Univ. Bordeaux, CNRS, Bordeaux INP, Laboratoire I2M, Talence |                                                                                                                                                          | <i>PCB</i>           |

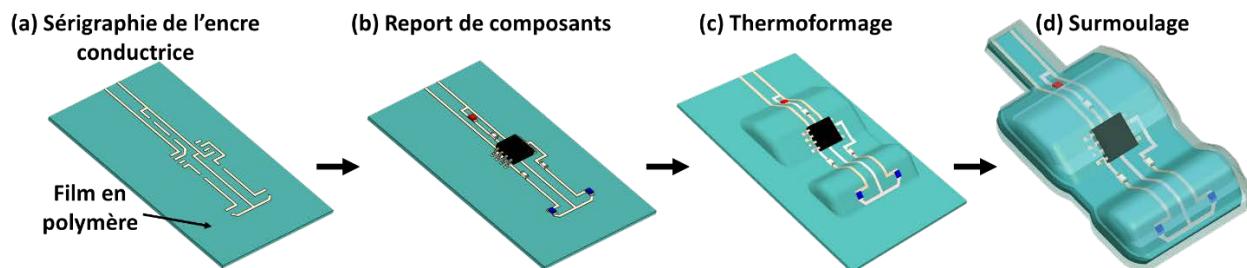

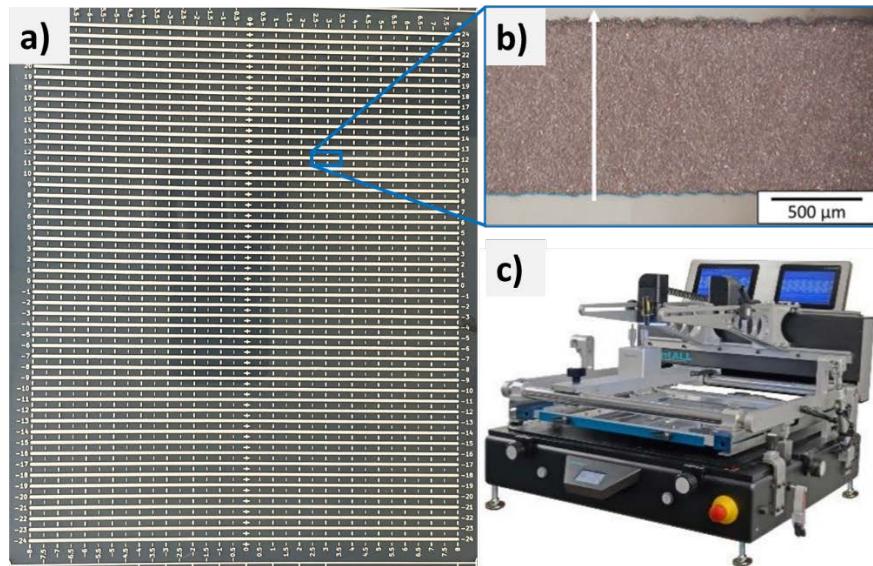

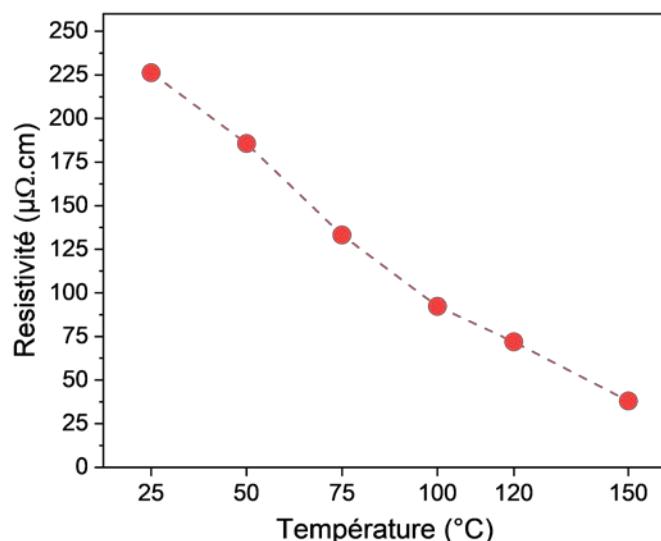

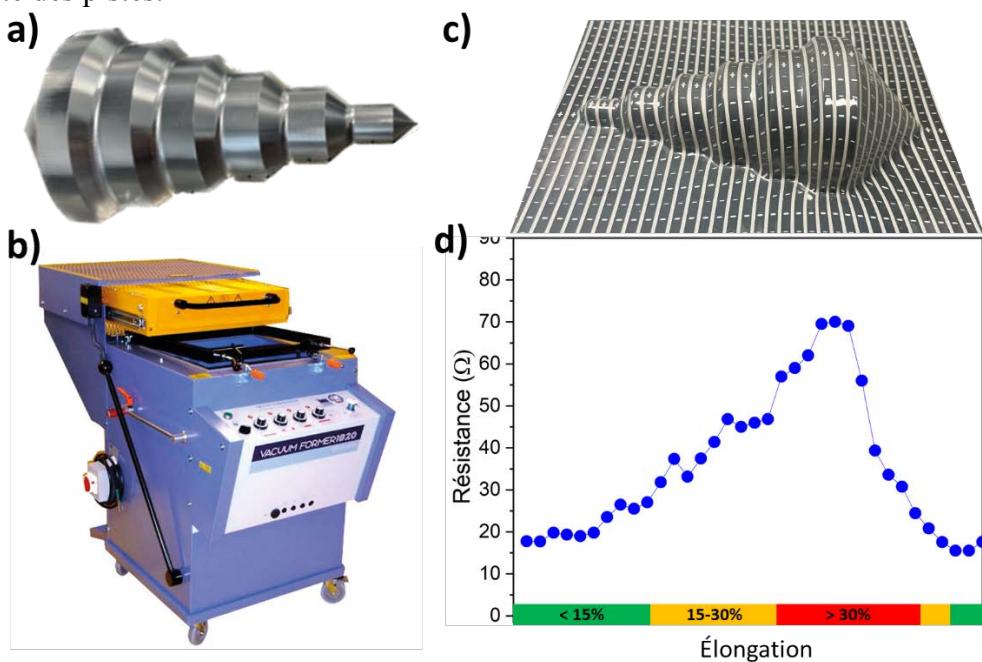

| <b>9 h 45</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>TP In-Mold Electronics : Étude de circuits imprimés 3D avec encre à matrice organique biosourcée</b>                                                  | <b>P4</b>            |

| <sup>1</sup> T. Gerges, <sup>1</sup> V. Semet, <sup>1</sup> P. Lombard, <sup>2</sup> J-Y Charneau, <sup>1</sup> B. Allard, <sup>1</sup> M. Cabrera<br><sup>1</sup> INSA Lyon, Université Claude Bernard Lyon 1, Ecole Centrale de Lyon, CNRS, Ampère, UMR 5005, Villeurbanne<br><sup>2</sup> INSA Lyon, IMP, UMR 5223, 01100 Bélgirate                                                                                                                                                              |                                                                                                                                                          | <i>CIMIRLY</i>       |

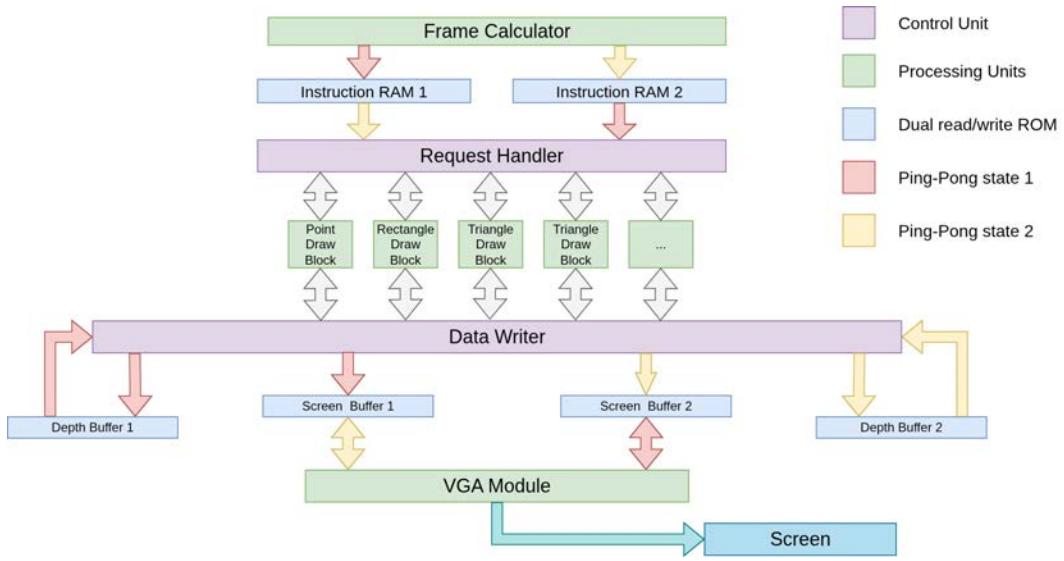

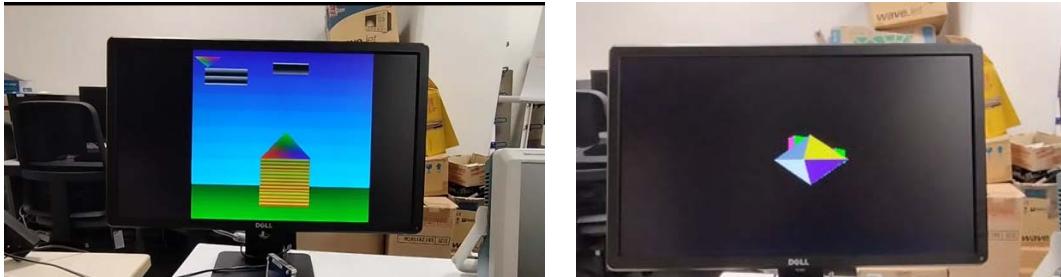

| <b>9h 50</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>Concevoir un GPU en projet microélectronique</b>                                                                                                      | <b>P5</b>            |

| C. Bou Tanos, J. Marqueti, L. Fesquet<br><i>Grenoble INP - Phelma, Université Grenoble Alpes, Grenoble</i>                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                          | <i>CIME-NANOTECH</i> |

**Cybersécurité**

|                                                                                                                 |                                                                                                                                                                            |             |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| <b>9 h 55</b>                                                                                                   | <b>Fautes intentionnelles ou non, depuis l'impact de l'environnement radiatif naturel jusqu'à la cyber sécurité : les enjeux de microélectronique</b>                      | <b>O6</b>   |

| Y. Helen<br><i>DGA, Dpt MI 136 La Roche Marguerite, 35170 Bruz</i>                                              |                                                                                                                                                                            |             |

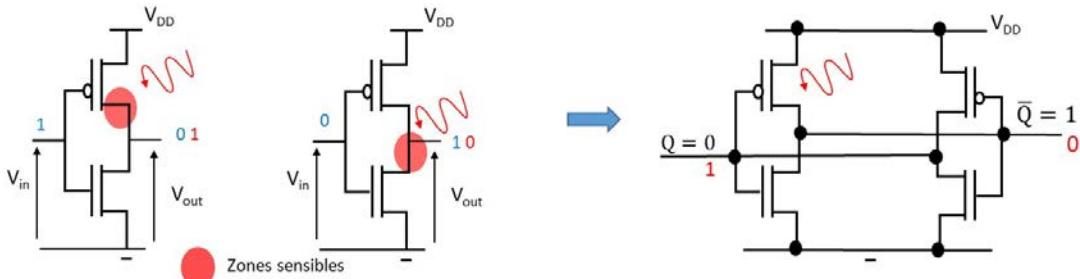

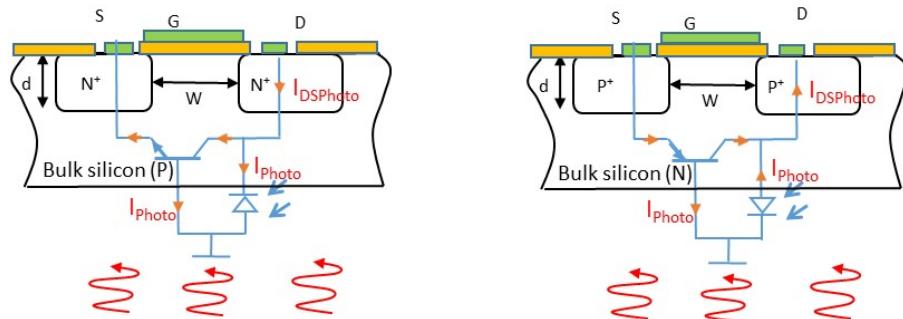

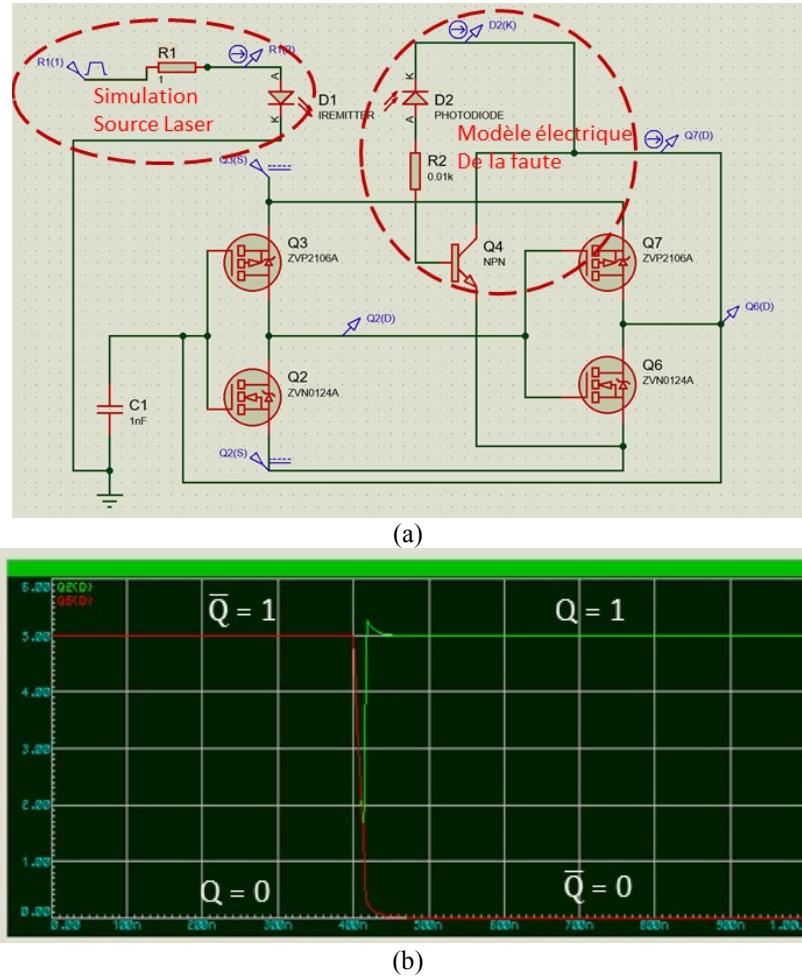

| <b>10 h 15</b>                                                                                                  | <b>Simulation électrique de l'injection de faute par laser dans une cellule mémoire SRAM : une approche à la sensibilisation à la cybersécurité matérielle en BUT GEII</b> | <b>P6</b>   |

| L. Pichon<br><i>IETR, IUT GEII, Rennes</i>                                                                      |                                                                                                                                                                            | <i>CCMO</i> |

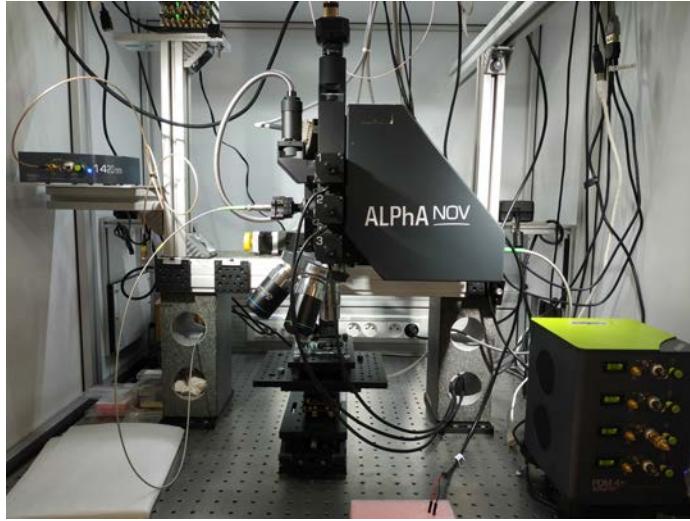

| <b>10 h 20</b>                                                                                                  | <b>Injection de faute par laser sur microcontrôleur : du silicium à la programmation</b>                                                                                   | <b>P7</b>   |

| L. Claudepierre, E. R. Ferrucho-Alvarez, L. Le Brizoual, L. Pichon<br><i>IETR, Université de Rennes, Rennes</i> |                                                                                                                                                                            | <i>CCMO</i> |

**10 h 25 TERO-PUF optimisé pour l'étalonnage sur Intel MAX-10 pour des PUF faibles et robustes**

P8

<sup>1,2</sup>K. Vicuña, <sup>3</sup>K. Foglia, <sup>1</sup>B. Sreejith, <sup>1</sup>F. Amiel, <sup>1</sup>L. Trojman

<sup>1</sup>Institut Supérieur d'Électronique de Paris (Isep), LISITE, Paris

<sup>2</sup>Département d'informatique, de modélisation, d'électronique et de génie des systèmes, Université de Calabre, Italie

<sup>3</sup>Département de mathématiques et d'informatique, Université de Calabre, Italie

CEMIP

**10h30 PAUSE- DÉMONSTRATIONS - POSTERS**

*Services Centraux*

**11 h00 Rapport d'activité des Services Nationaux du CNFM**

O7

P. Benoit

PCM

CNFM-PCM / Université Montpellier

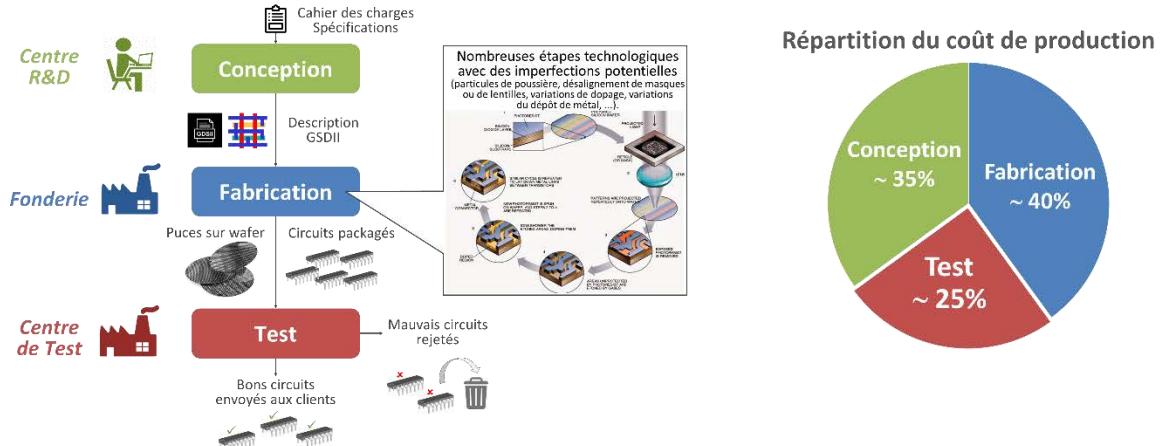

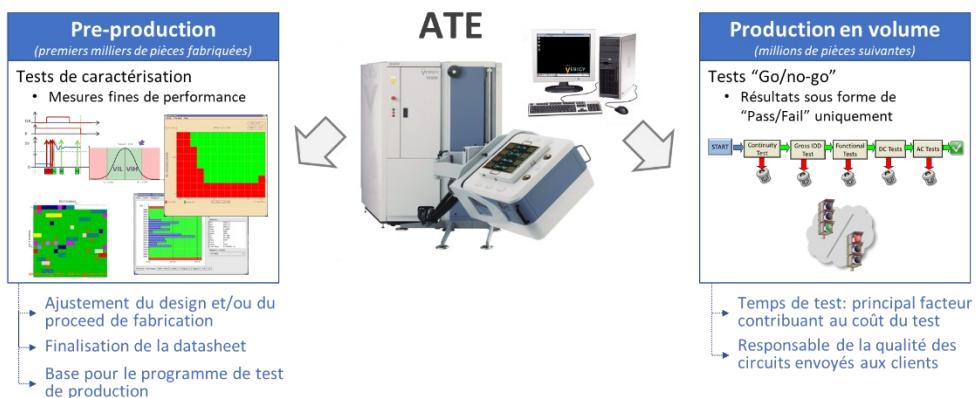

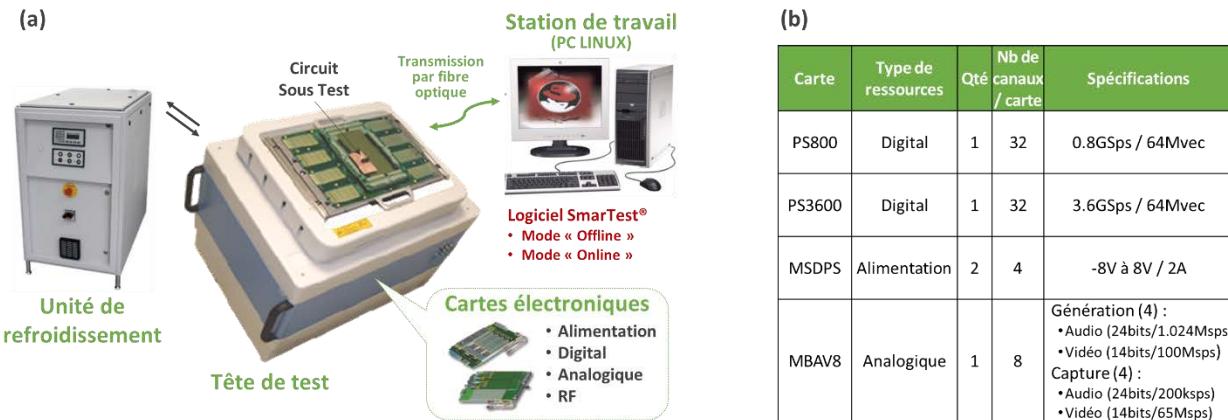

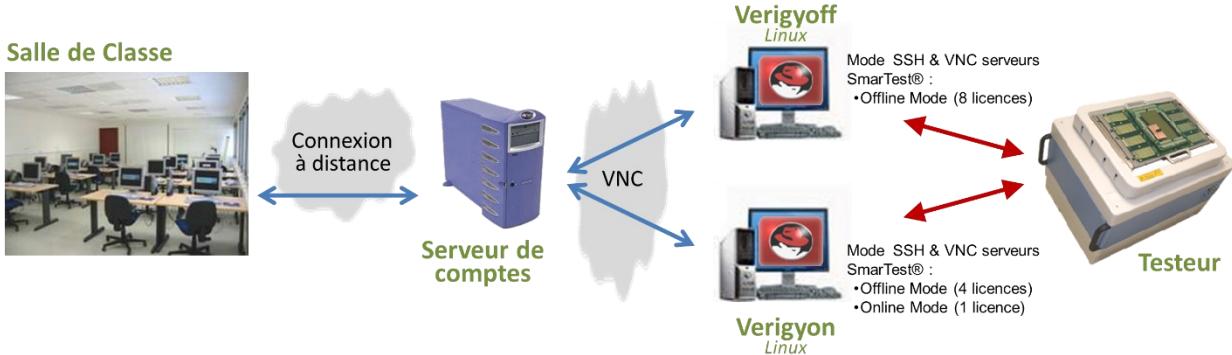

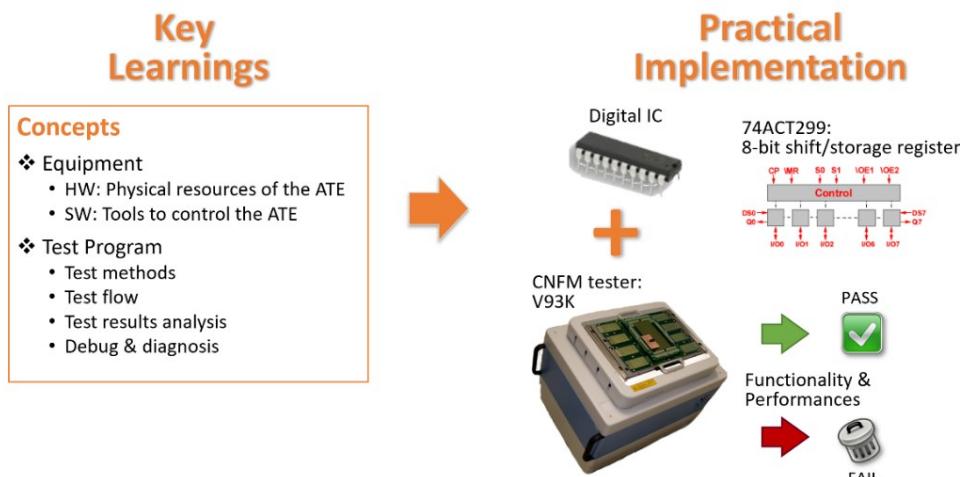

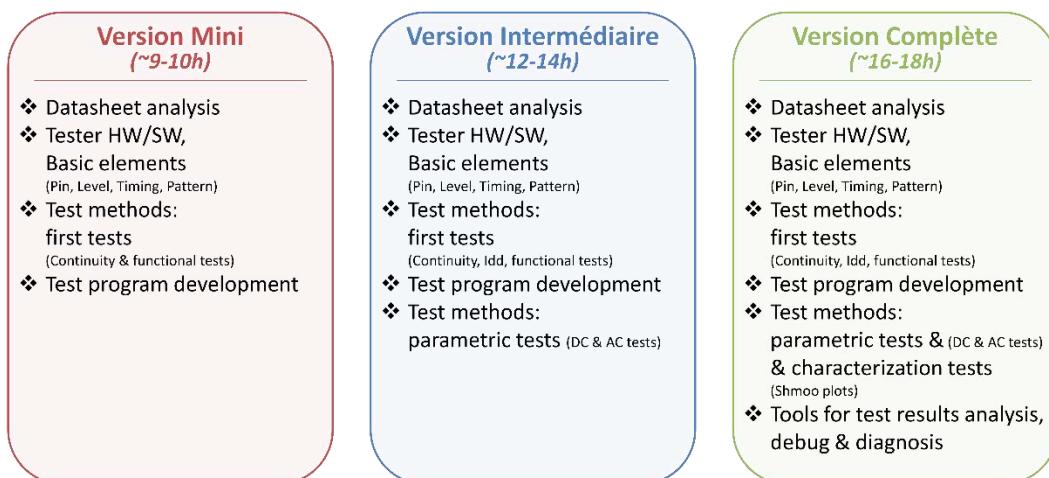

Formation au test industriel des circuits intégrés digitaux : une offre « clé en main »

P9

F. Azais, M. Comte, M.-L. Flottes, P. Leloup

PCM

LIRMM (UMR CNRS/Université de Montpellier), Montpellier

Enseignement de la conception des Circuits Intégrés Numériques à Polytech Montpellier

J.-M. Gallière, P. Maurine, P. Benoit

P10

Polytech Montpellier, Université de Montpellier, Montpellier

PCM

**11h30 Nouveaux outils pour la conception des cartes**

O8

M. Brochet

Senior Executive Account Manager, Cadence Design Systems, France

**12 h DEJEUNER**

**13 h 45 EXCURSION MALOUINE**

*Technologie*

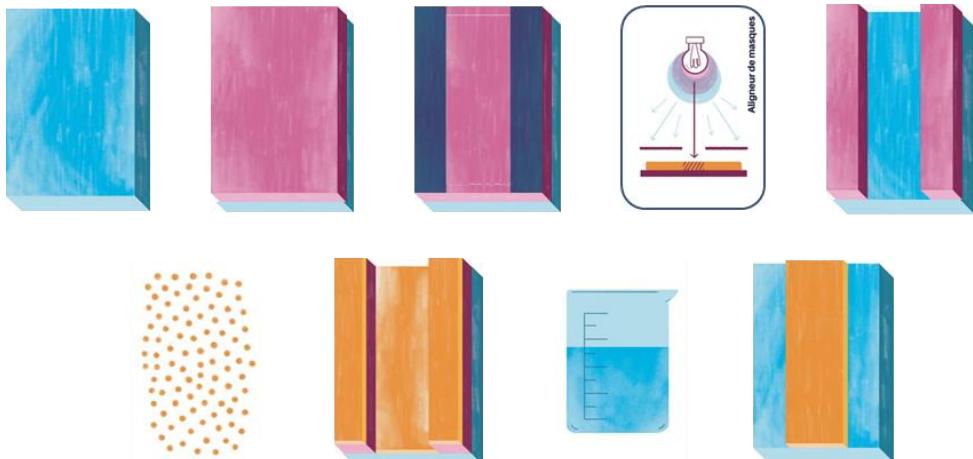

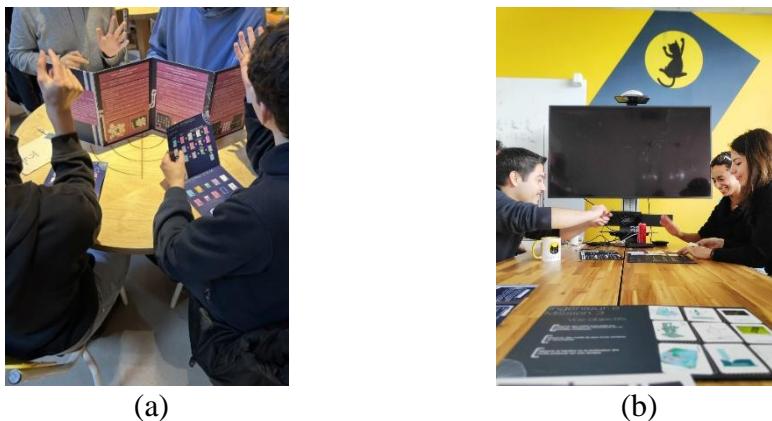

**16 h 00 La Fabrique du Nano : Le Jeu !**

P11

<sup>1</sup>N. Lidgi-Guigui, <sup>2</sup>J. Bobroff, <sup>2</sup>F. Bouquet, <sup>3</sup>N. Piñeros, <sup>2</sup>C. Hinnoveanu, <sup>2</sup>Z. Lemaire

<sup>1</sup>LSPM, CNRS – Université Sorbonne Paris Nord, Villeurbanne, France

<sup>2</sup>Université Paris-Saclay, CNRS, Laboratoire de Physique des Solides, 91405 Orsay

<sup>3</sup>Ludomaker LudoMaker, LLHS et laboratoire EXPERICE, Université Sorbonne Paris Nord, Villeurbanne

PMIPS

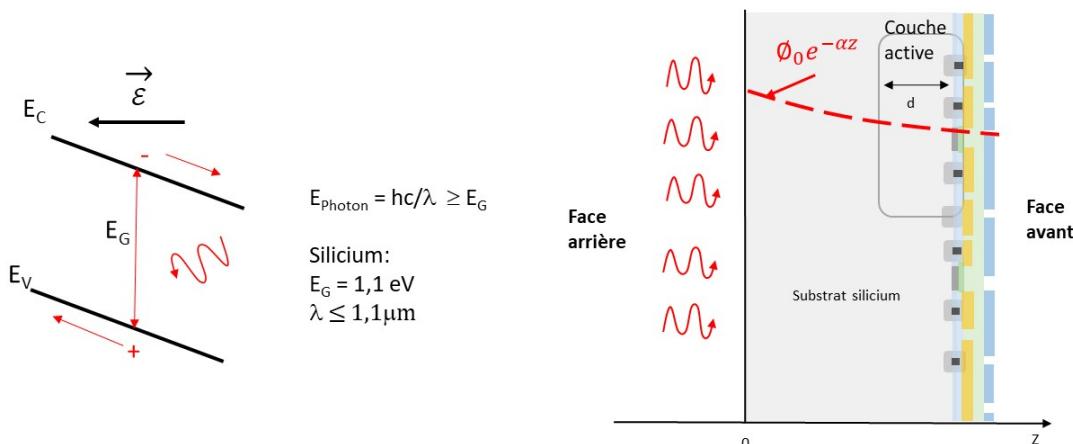

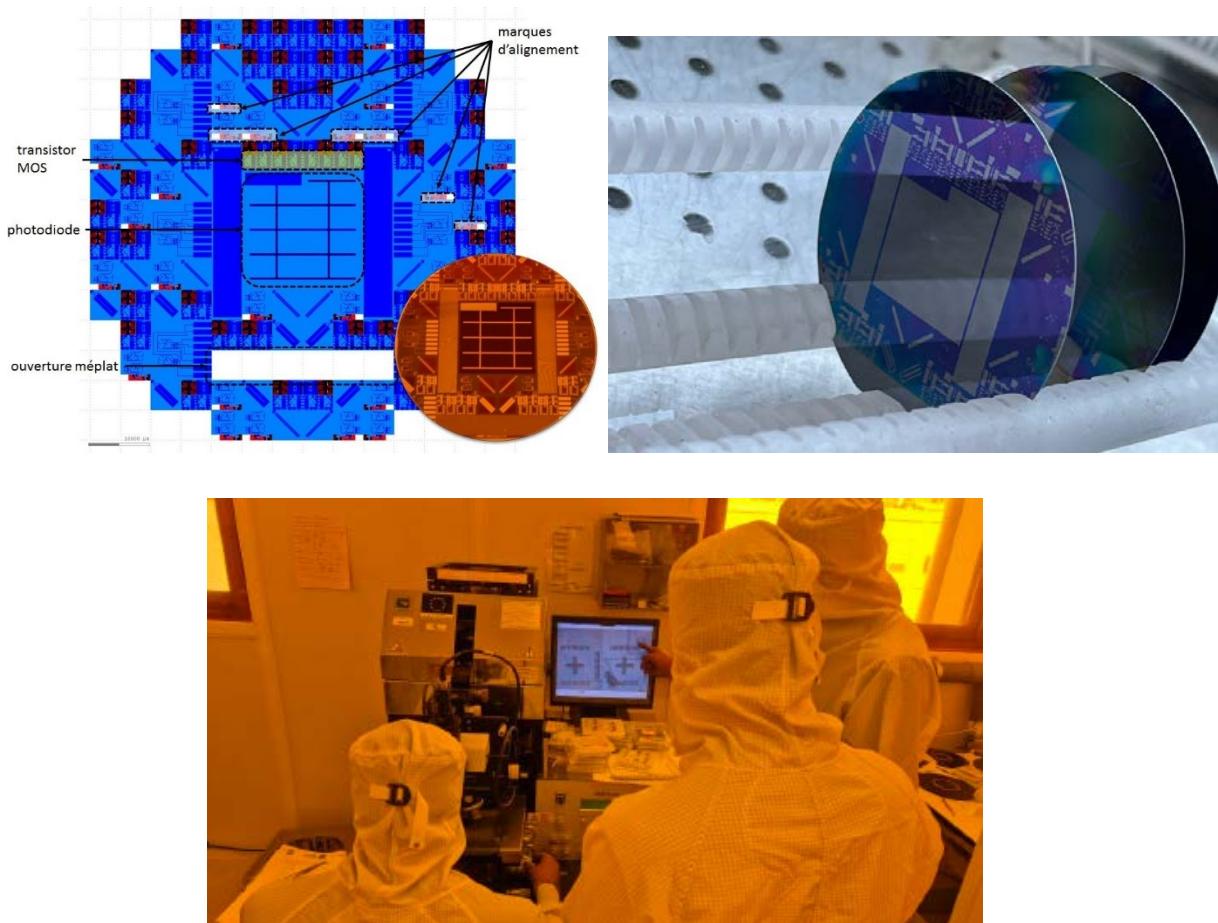

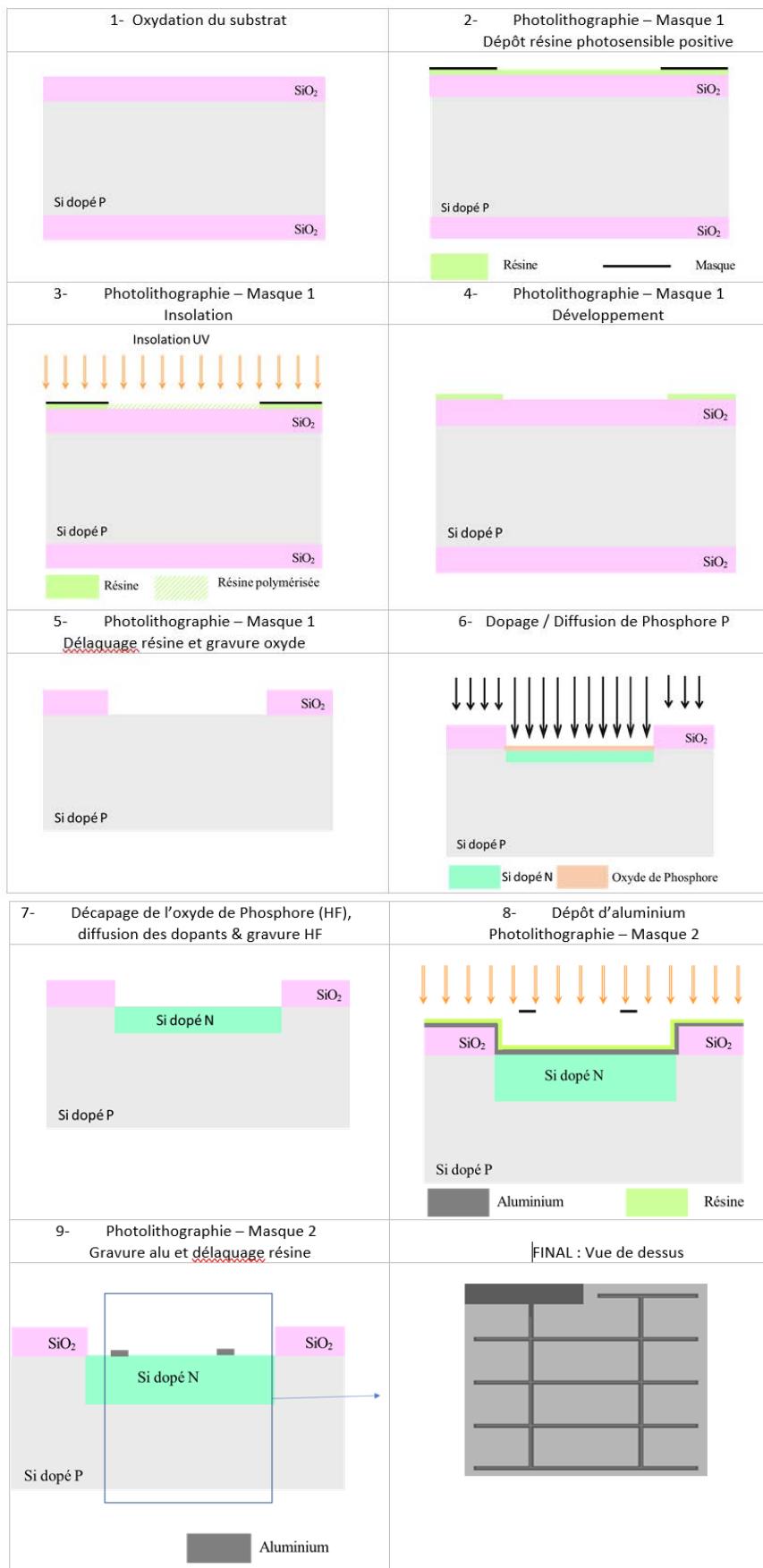

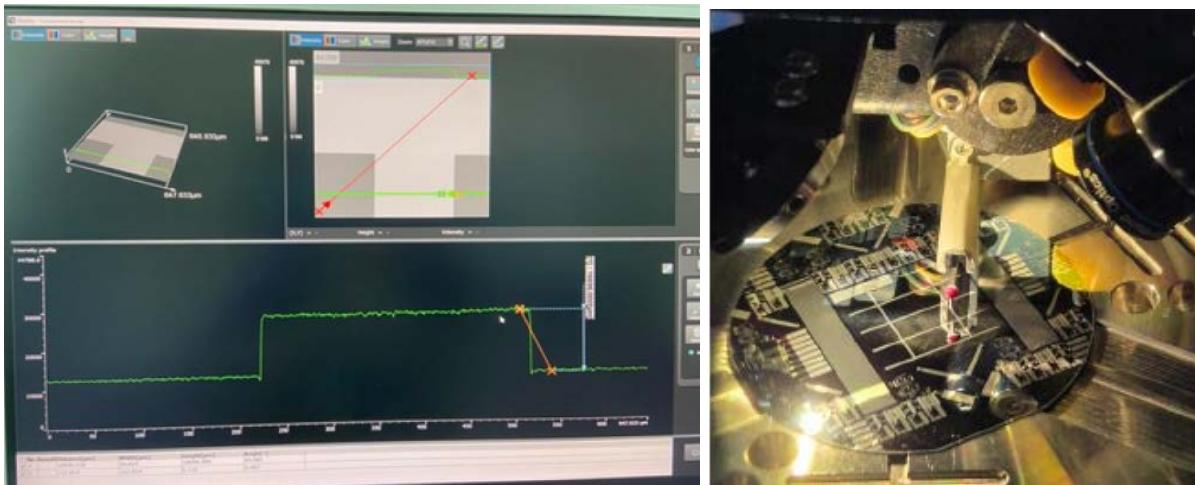

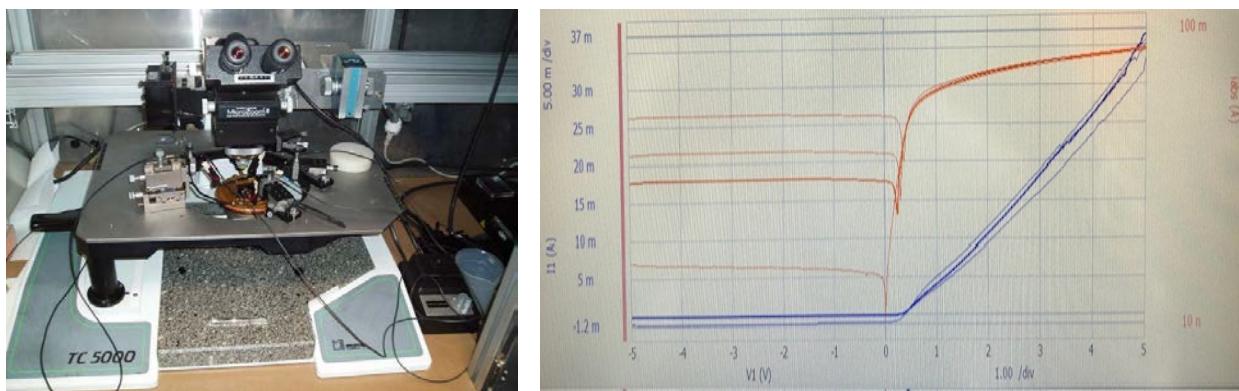

**16 h 05 Saé en salle blanche pour les étudiants de BUT3 GEII : fabrication et caractérisation d'un capteur de luminosité**

P12

<sup>1,2</sup>A.-C. Salaün, <sup>1,2</sup>R. Rogel, <sup>1</sup>C. Lebreton, <sup>1</sup>O. De Sagazan, <sup>1,2</sup>L. Pichon

<sup>1</sup>IETR et pôle CNFM de Rennes (CCMO), Université de Rennes

<sup>2</sup>IUT de Rennes, département GEII, Rennes

CCMO

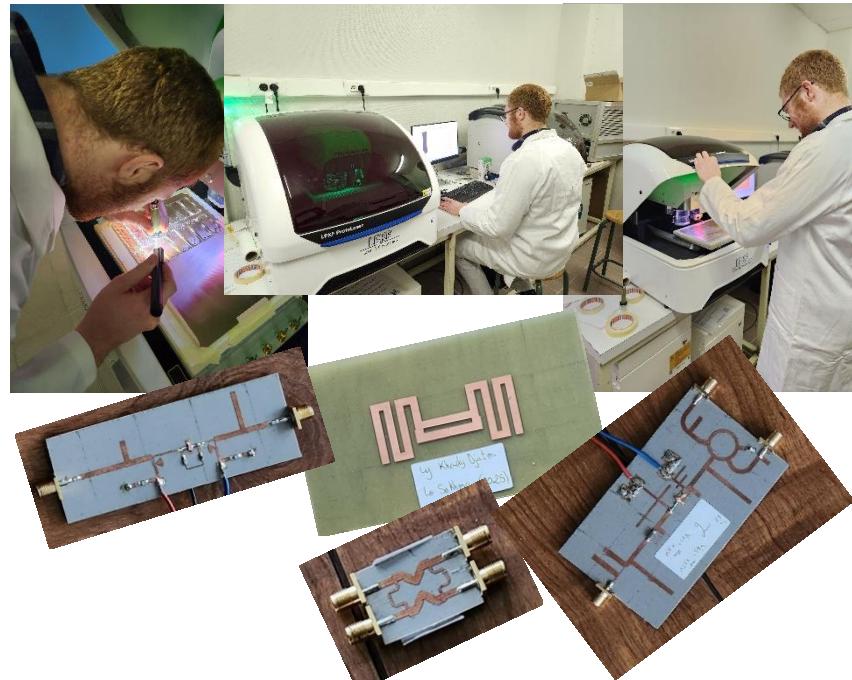

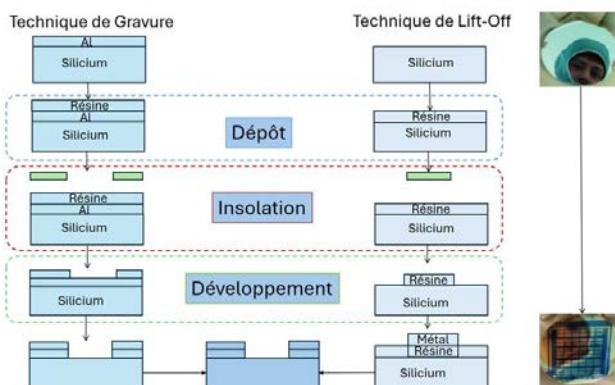

**16 h 10 De la photolithographie chimique à la gravure laser : une nouvelle ère pour la réalisation de circuits RF au sein du Master Réseaux et Télécommunications**

P13

<sup>1</sup>P. Laly, <sup>2</sup>V. Hoel, <sup>2</sup>M. Abou Daher, <sup>2</sup>F. Khenfer-Koummich, <sup>3</sup>V. Picquet

<sup>1</sup>IEMN Pôle C2EM Cité Scientifique, Villeneuve d'Ascq

<sup>2</sup>PLFM CNFM Université de Lille, Cité Scientifique, Villeneuve d'Ascq

PLFM

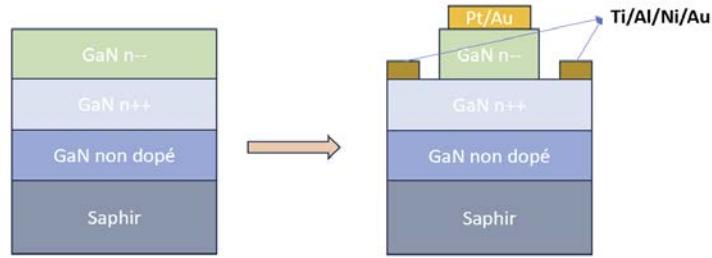

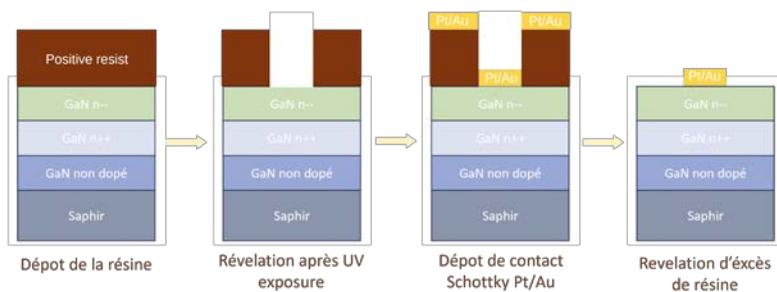

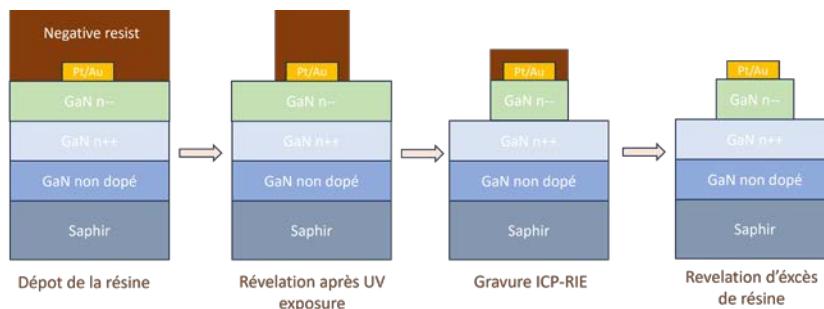

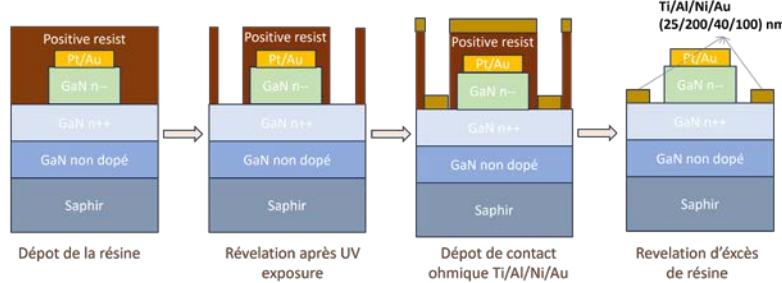

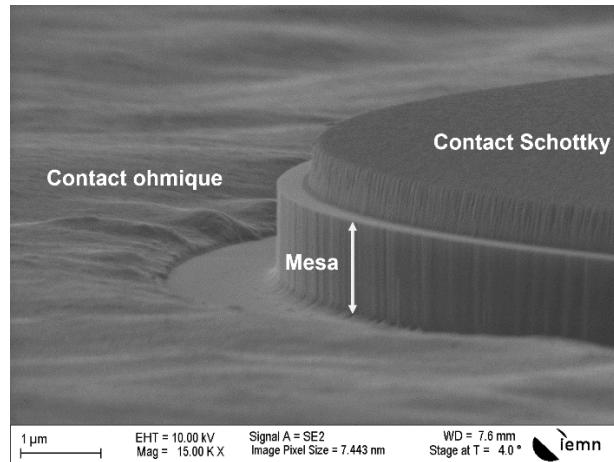

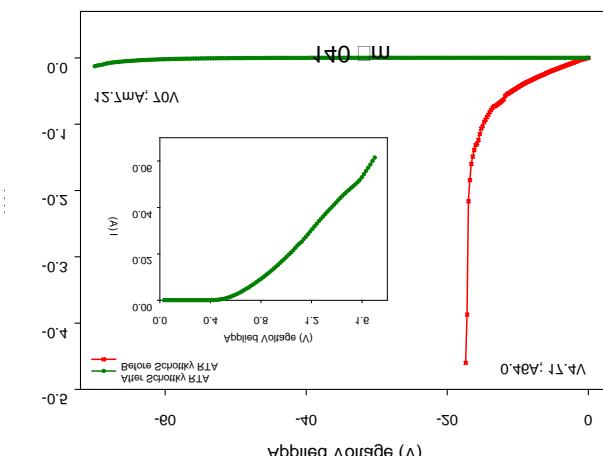

**16 h 15 Fabrication et caractérisation de diodes Schottky GaN dans un TP innovant au sein du PLFM de Lille**

P14

M. Laddada, I. Nhaila, S. Ouendi, Y. Roelens, V. Hoel, M. Abou Daher

IEMN, Université de Lille, Villeneuve d'Ascq

PLFM

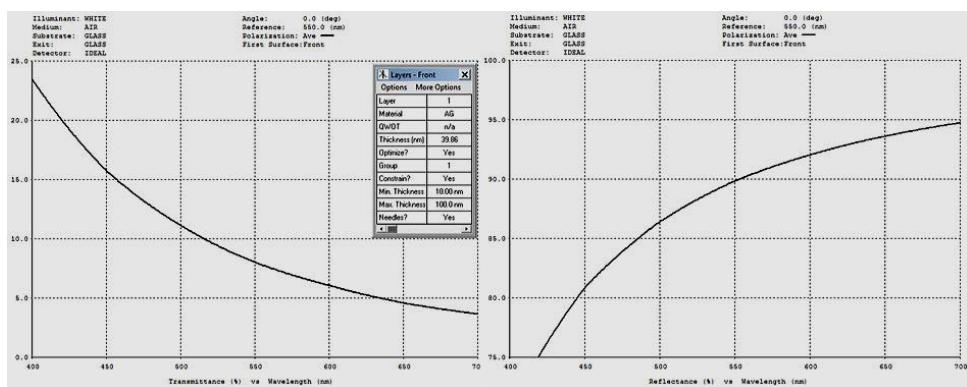

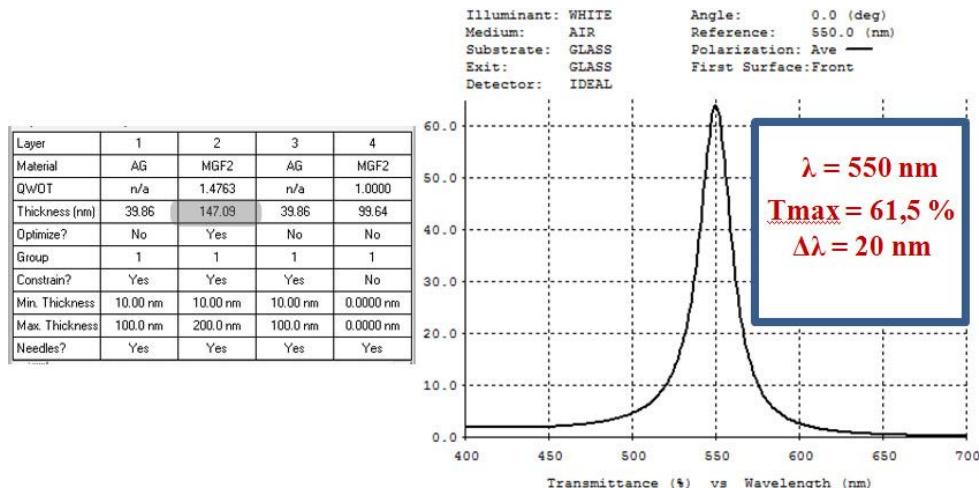

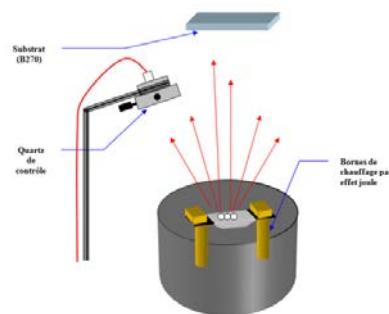

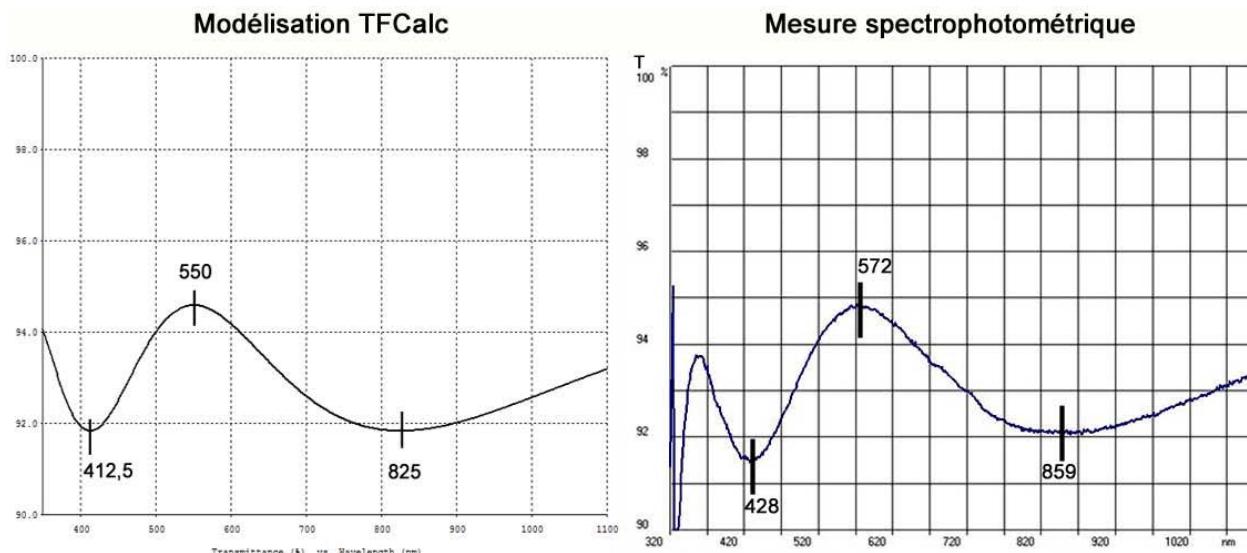

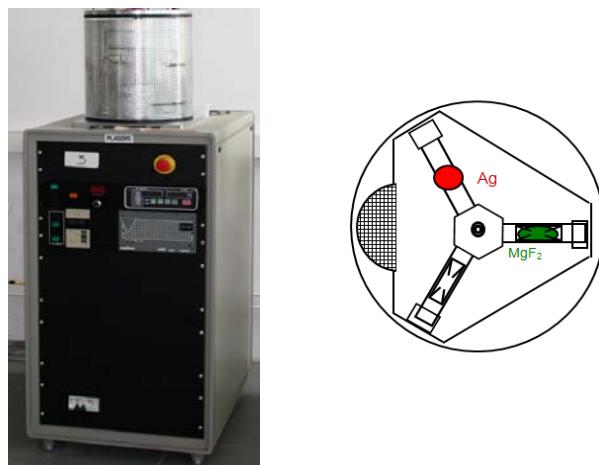

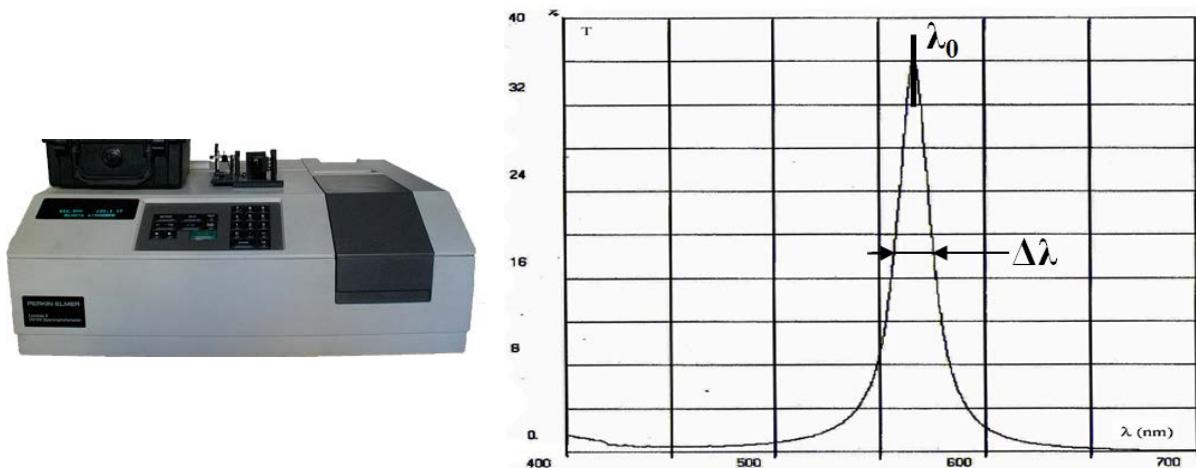

**16 h 20 Réalisation d'une fonction optique filtrante par dépôt de couches minces**

P15

M. Coué, G. Agnus

Université de Paris-Saclay, Palaiseau

PMIPS

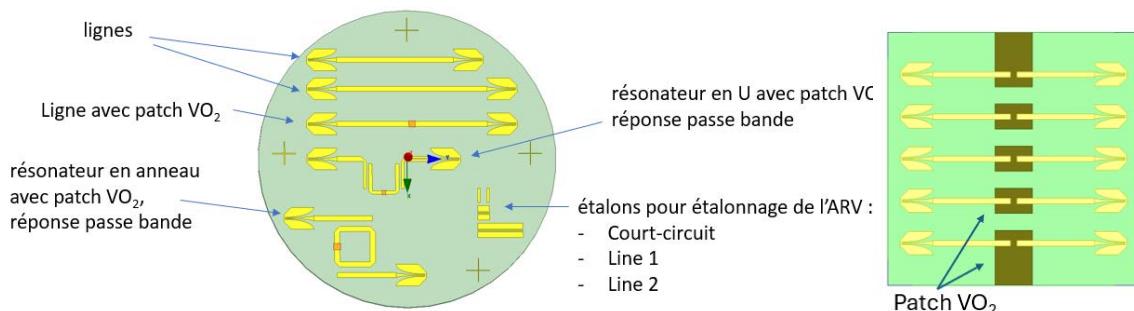

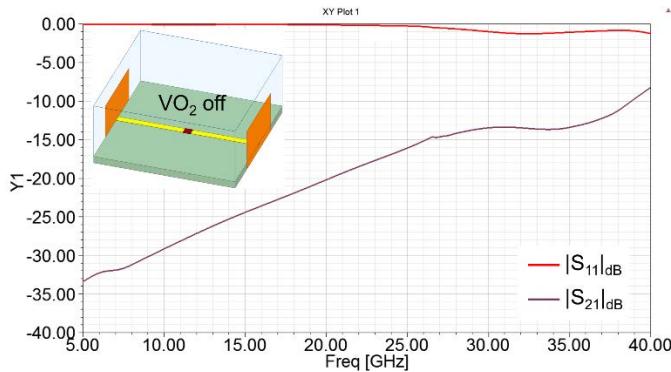

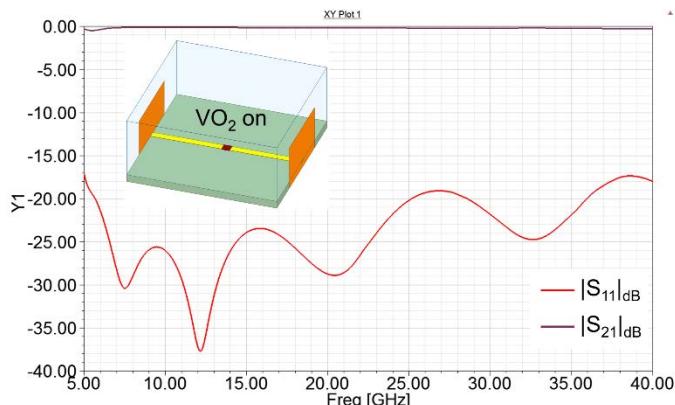

**16 h 25 Lignes et résonateurs micro-ondes planaires commutables par dépôt VO<sub>2</sub> pour l'enseignement de la conception, des techniques de dépôt et de la caractérisation de dispositifs micro-ondes**

P16

<sup>1</sup>B. Henriot, <sup>2</sup>M. Gireau, <sup>1</sup>G. Mastouri, <sup>1</sup>O. Tantot, <sup>2</sup>F. Dumas-Bouchiat,

<sup>2</sup>C. Champeaux, <sup>1</sup>A. Périgaud, <sup>1</sup>D. Passerieux, <sup>1</sup>B. Barelaud, <sup>1</sup>S. Verdeyme

<sup>1</sup>XLIM, UMR 7252, Université de Limoges/CNRS, 123 av A. Thomas, 87060 Limoges

<sup>2</sup>IRCER, UMR 7315, Université de Limoges/CNRS, 12 Rue Atlantis, 87068 Limoges

PLM

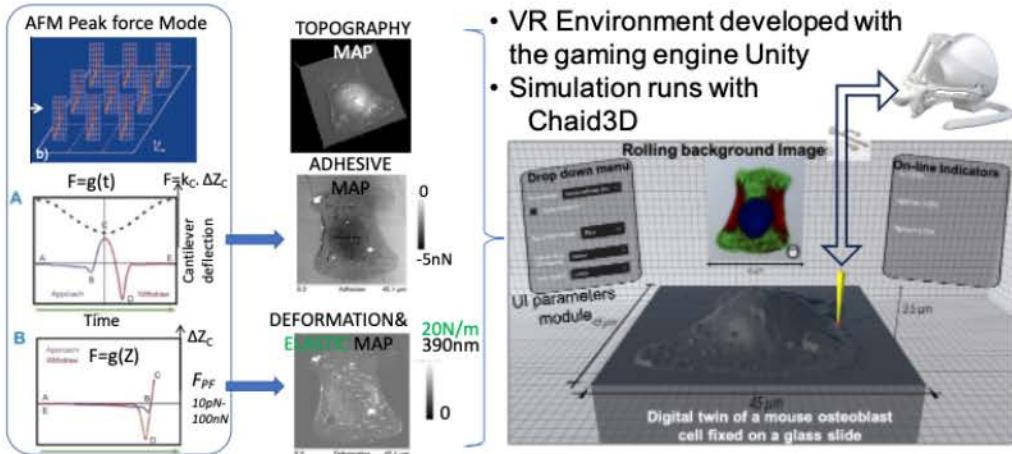

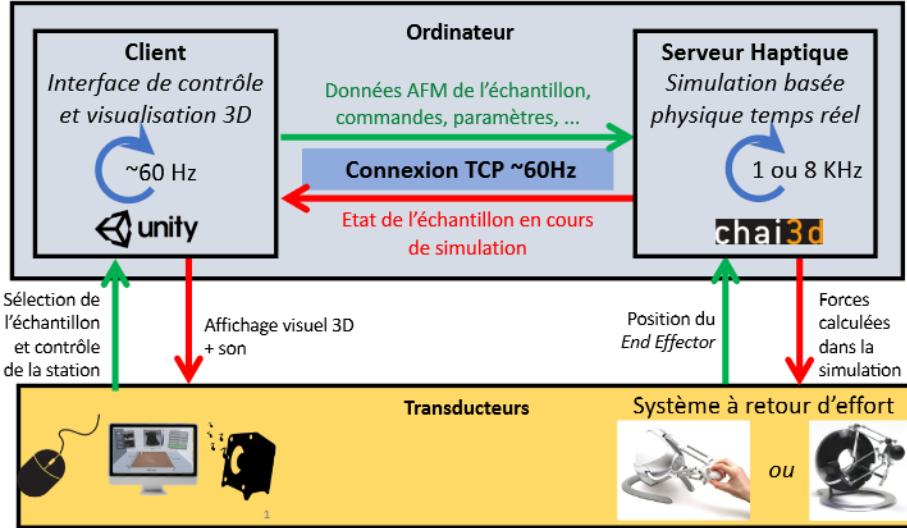

**16 h 30 La station pédagogique et interactive « NanoEnactive » basée sur des jumeaux numériques d'échantillons à échelle nanométrique**

P17

<sup>1</sup>F. Marchi, <sup>2</sup>N. Castagné, <sup>3</sup>A. Bsiesy, <sup>3</sup>L. Mambert, <sup>3</sup>N. Guerre-Chaley, <sup>3</sup>A. Borget,

<sup>3</sup>R. Paquet

<sup>1</sup>Institut Néel, Université Grenoble Alpes, Grenoble

<sup>2</sup>Université Grenoble Alpes, Grenoble INP, GIPSA Lab, Grenoble

<sup>3</sup>CIME Nanotech, Université Grenoble Alpes, Grenoble

CIME-NANOTECH

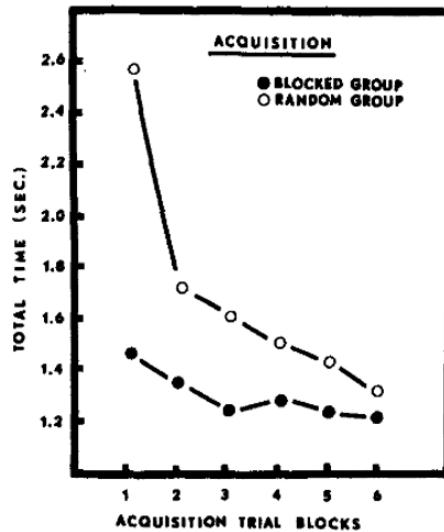

**16 h 35 L'apport des sciences cognitives pour l'apprentissage procédurale en salle blanche.**

P18

<sup>1,2</sup>M. Turpin, <sup>2</sup>C. Tordet, <sup>1</sup>F. Fabbri, <sup>2</sup>F. Zenasni, <sup>1</sup>G. Agnus

<sup>1</sup>Centre de Nanosciences et de Nanotechnologies (C2N), Université Paris-Saclay

<sup>2</sup>Laboratoire de Psychologie et d'Ergonomie Appliquée (LaPEA), Université Paris Cité

PMIPS

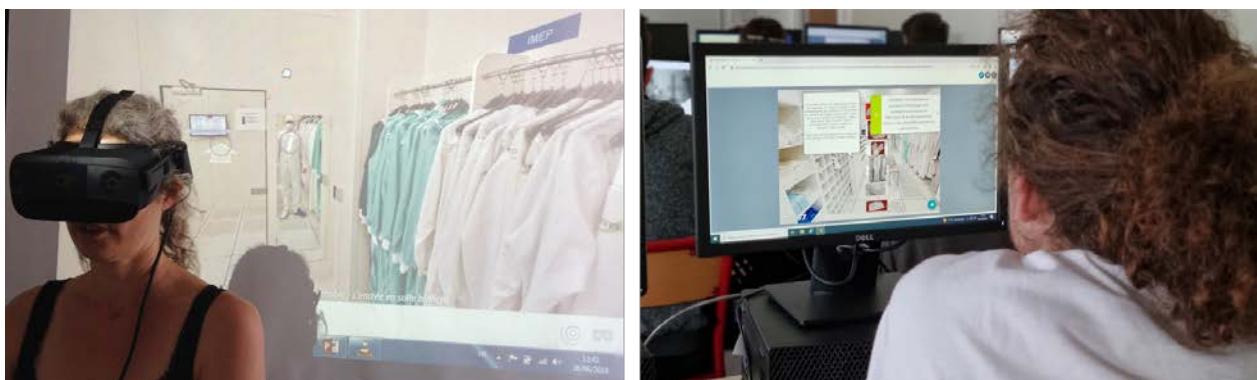

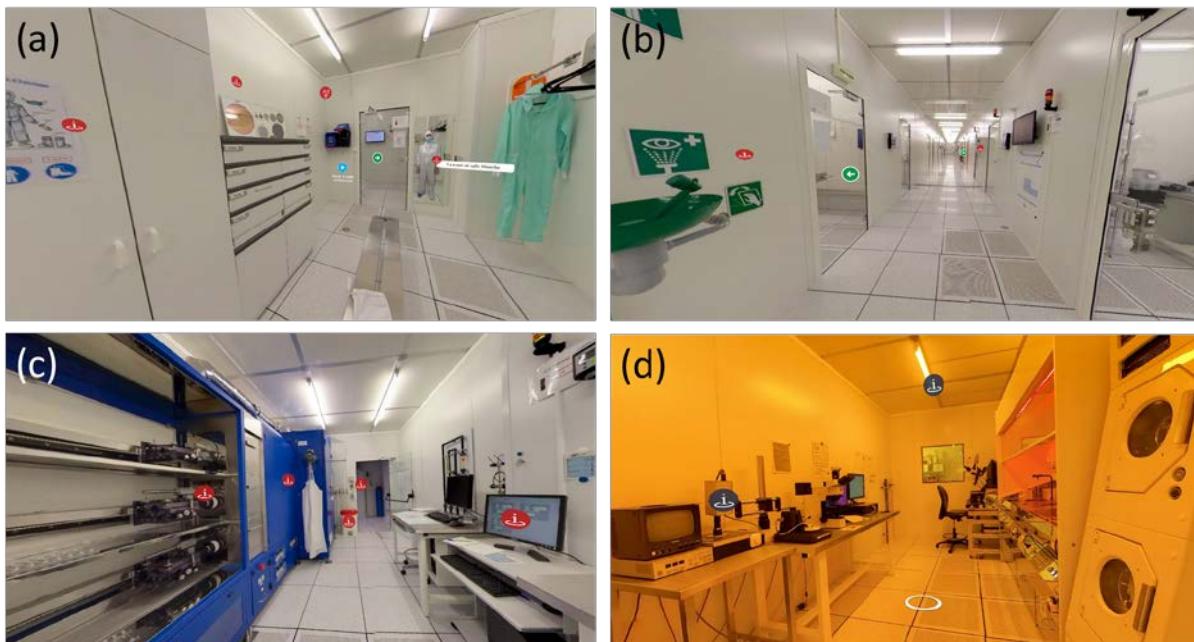

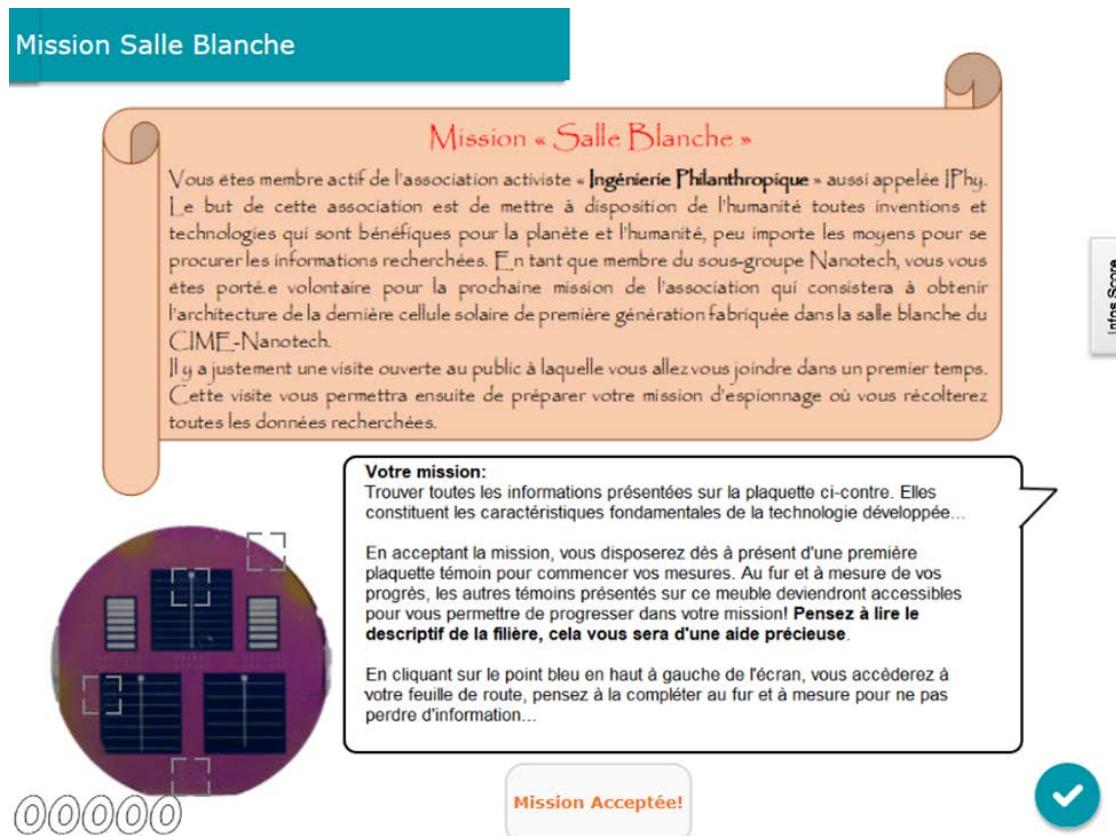

**16 h 40 La réalité virtuelle au service de l'apprentissage en salle blanche : le projet "Mission : Salle Blanche"**

P19

<sup>1</sup>C. Ternon, <sup>2</sup>K. Cauchois, <sup>3</sup>G. Cornu, <sup>4</sup>D. Constantin, <sup>3</sup>P. Arnaud

<sup>1</sup>Grenoble INP – Phelma, UGA, Grenoble

<sup>2</sup>Grenoble INP – Perform, UGA, Grenoble

<sup>3</sup>Maison Pour la Science en Alpes Dauphiné (MPLS-AD), Grenoble

<sup>4</sup>CIME Nanotech, Grenoble

CIME-NANOTECH

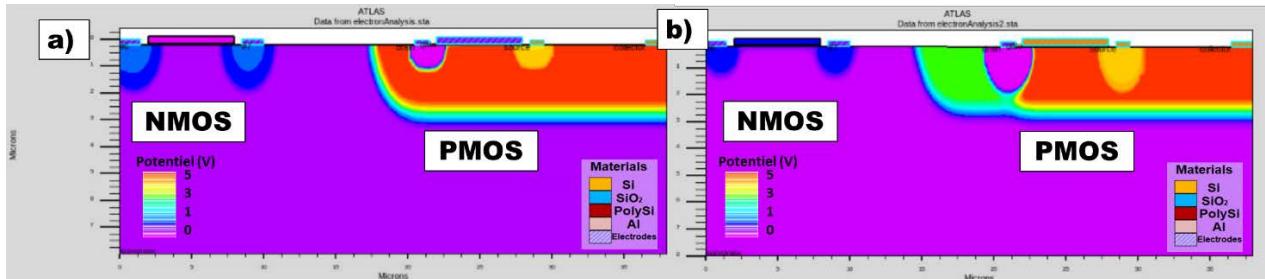

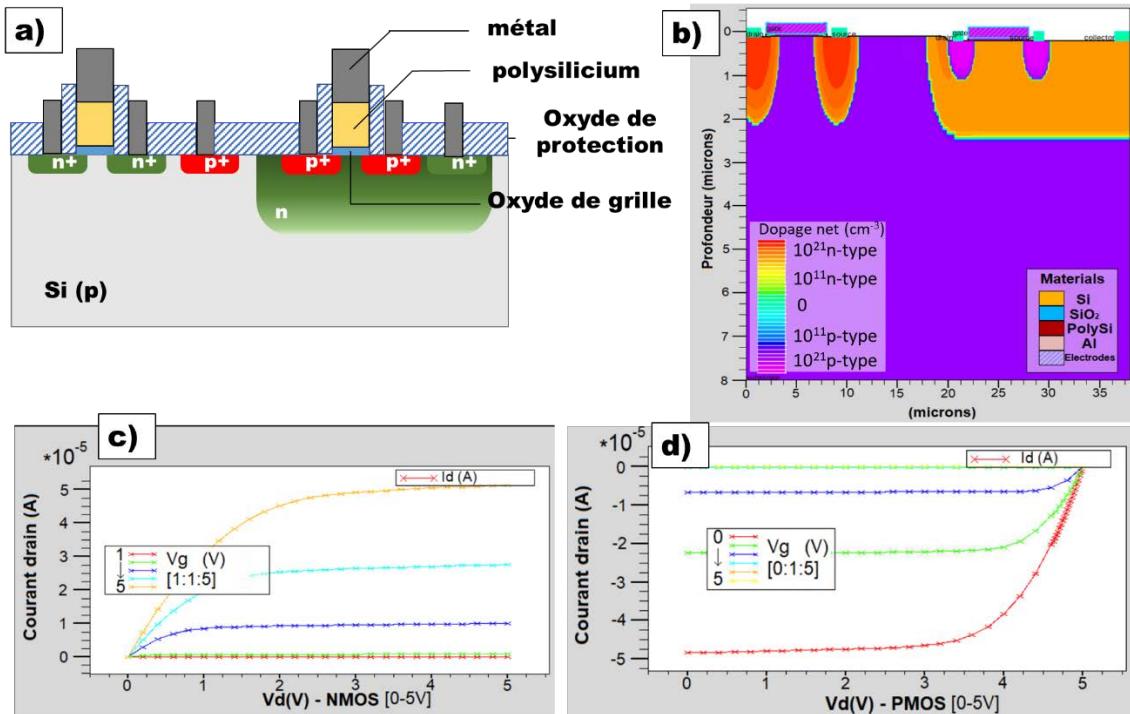

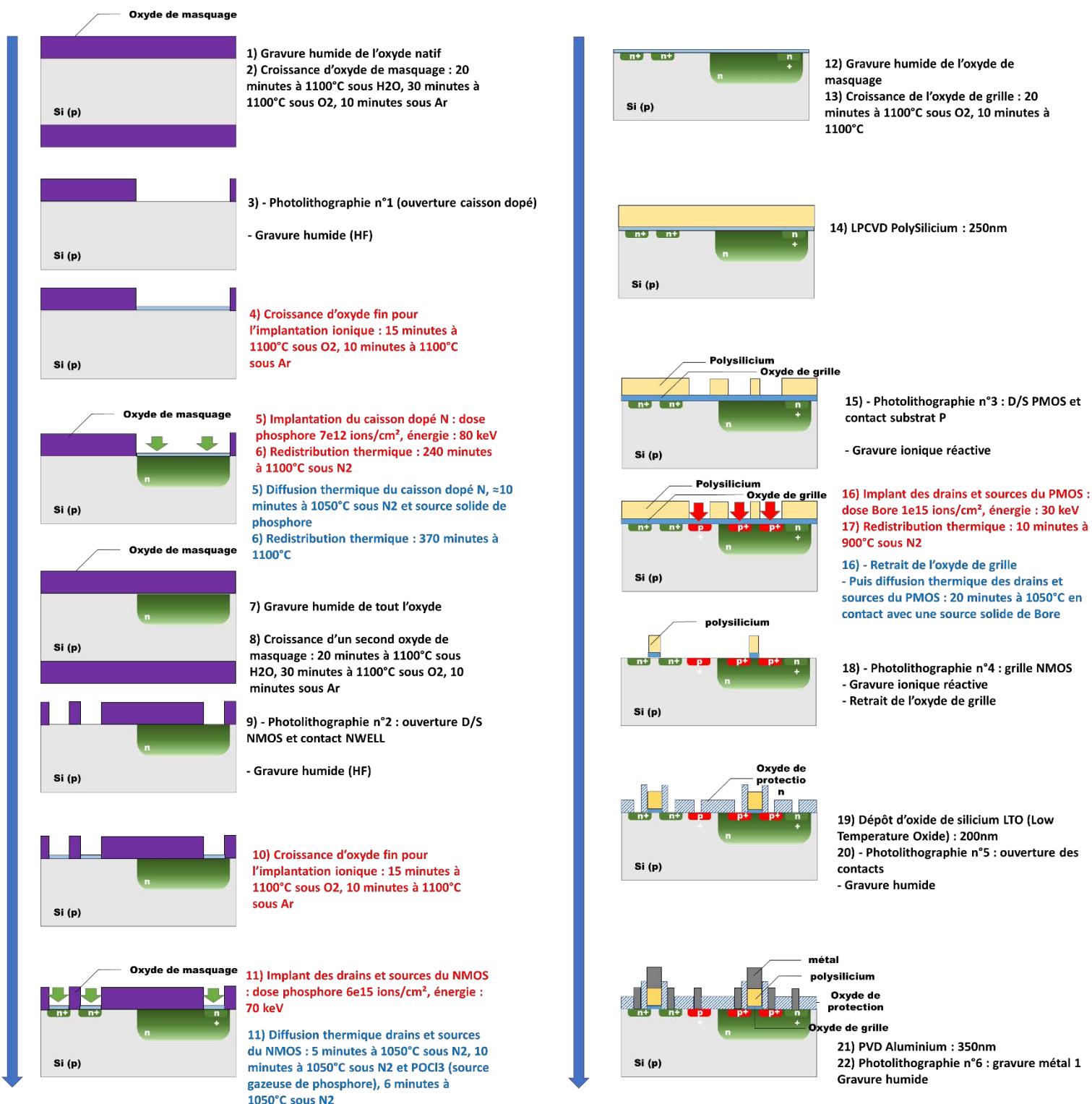

**16 h 45 Formation CMOS à l'AIME : évolution du procédé à l'aide de TCAD**

P20

R. Tan, J-B. Lincelles, M. Charnay, C. Capello, J. Schaeber, H. Azeroual,

I. Konate, O. Bernal, H. Tap, M. Respaud

AIME Toulouse

AIME

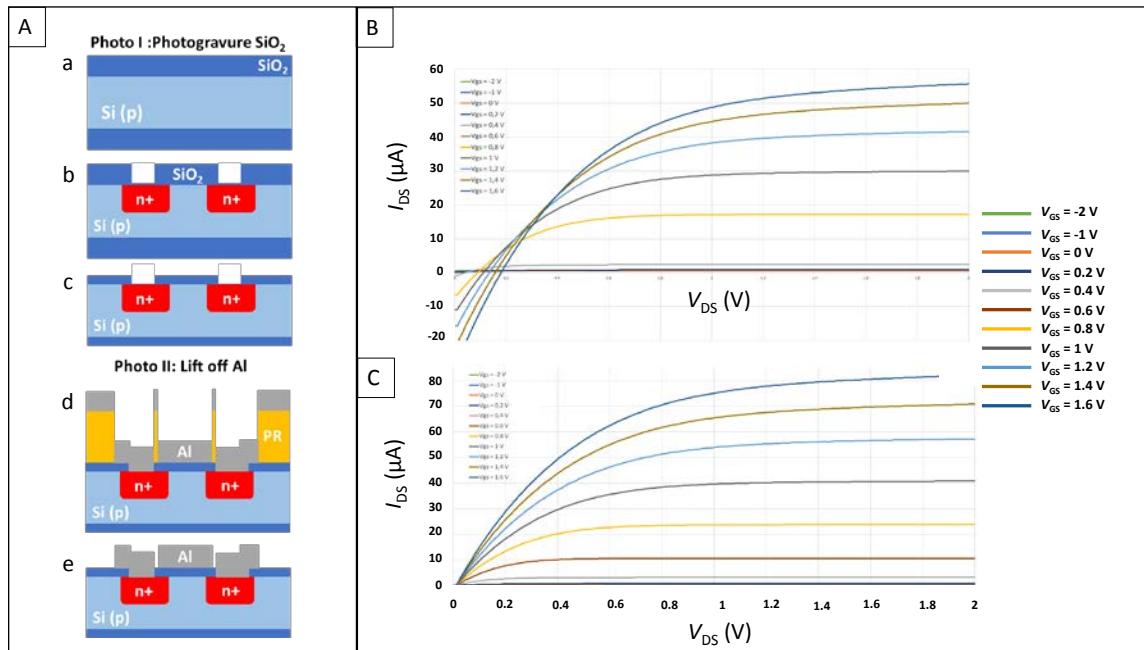

**16h 50 Procédé flash MOSFET : l'essentiel des procédés de micro-nanofabrication en deux photolithographies**

P21

G. Agnus, A. Hamadeh, R. Tan, Ch. Capello, Ch. Rouabhi, J. Schaeber, H. Azeroual,

I. Konate, J-B. Lincelles et M. Respaud

<sup>1</sup>Université de Paris Saclay, Palaiseau

<sup>2</sup>AIME, Toulouse

PMIPS/AIME

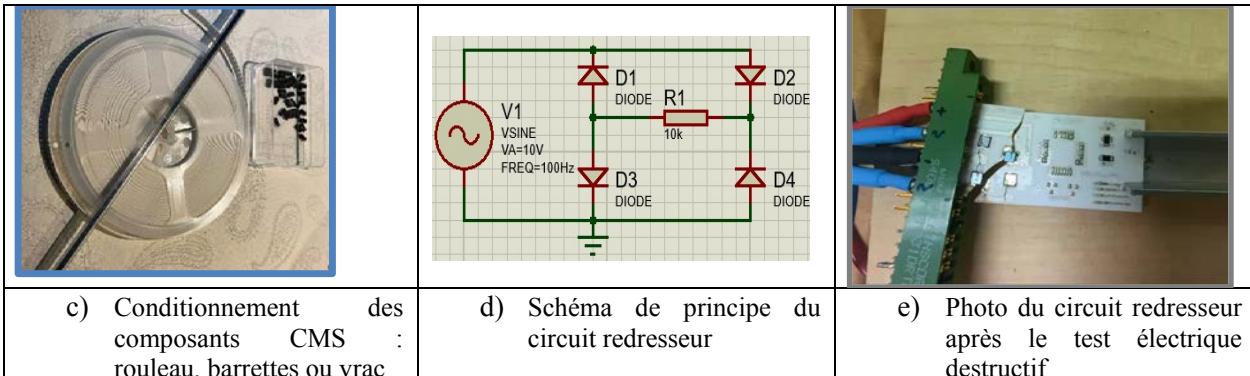

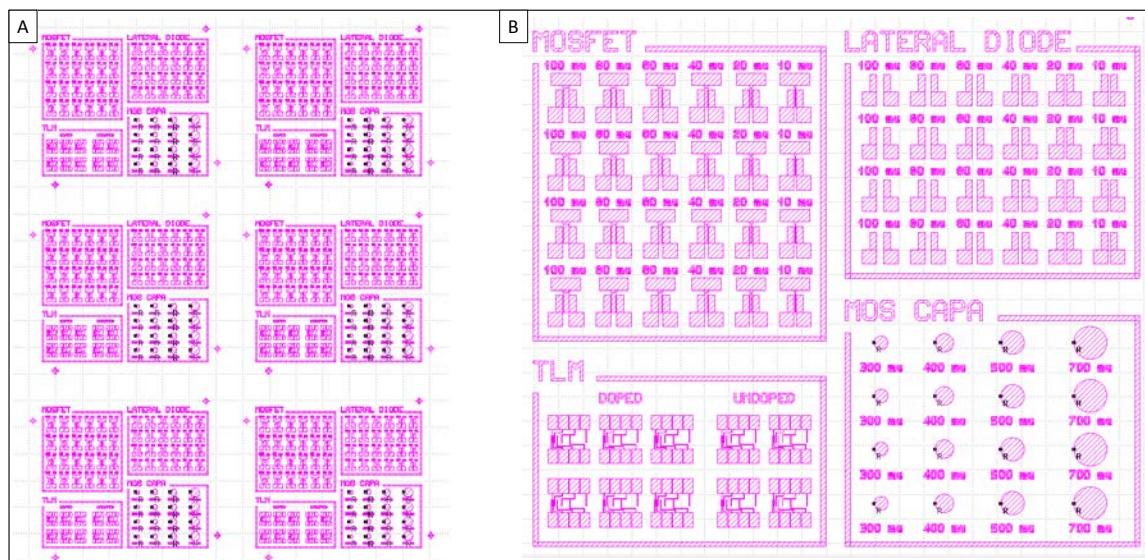

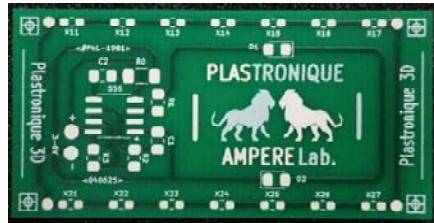

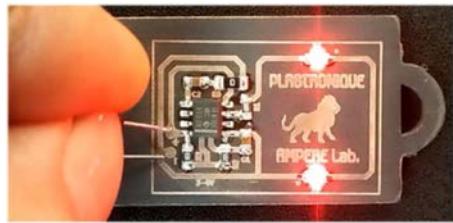

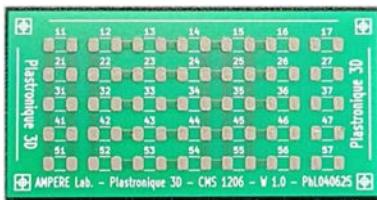

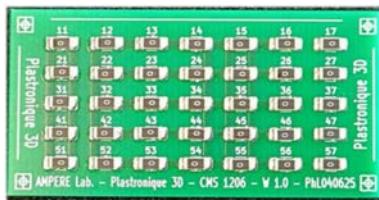

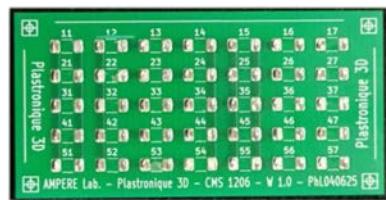

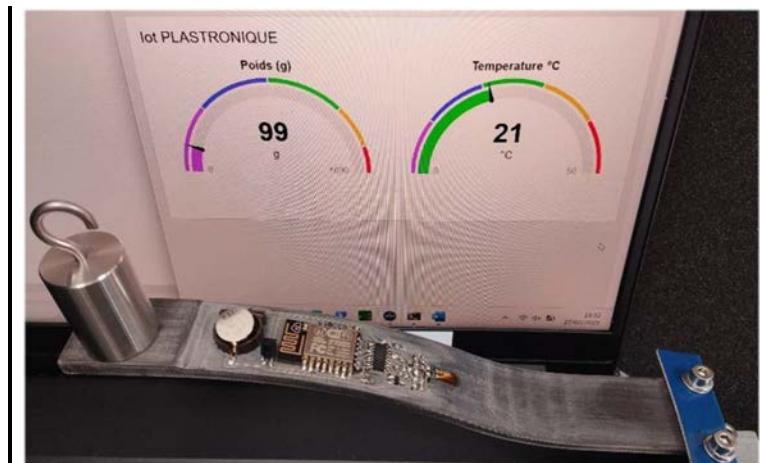

**16 h 55 Techniques et technologies d'assemblage des composants électroniques sur PCBA 2D vers les systèmes Plastronique 3D**

P22

P. Lombard, C. Orango, T. Gerges, B. Allard, M. Cabrera

Université de Lyon : Université Claude Bernard Lyon 1, CNRS, Ecole Centrale de Lyon, INSA de Lyon

Laboratoire AMPERE – UMR CNRS 5005 F-69621 Villeurbanne

CIMIRLY

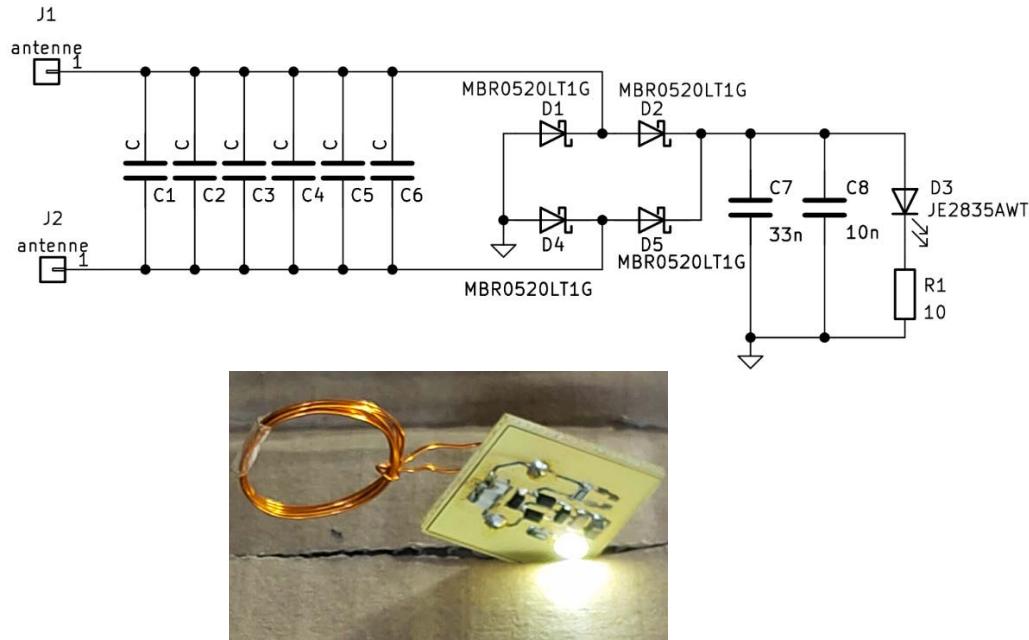

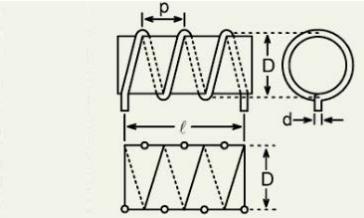

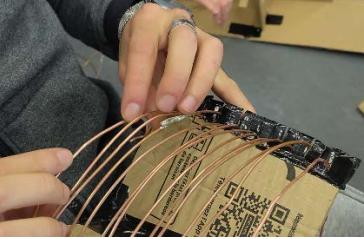

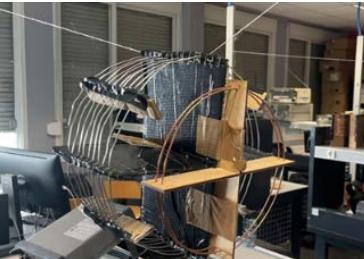

**17 h 00 BOBIN'ATHLON : mise en pratique de la transmission d'énergie sans fil (WPT) par le défi compétitif et l'apprentissage tutoré**

P32

<sup>1</sup>S.Hémour, <sup>2</sup>F. Champion, <sup>2</sup>D. Blanchard, <sup>3</sup>S. Reverdy, <sup>4</sup>J. Tomas

<sup>1</sup>IMS, IUT Bordeaux, dpt GEII, Université de Bordeaux, Bordeaux

<sup>2</sup>IUT de Bordeaux (Université de Bordeaux), département GEII, Gradignan

<sup>3</sup>CAP ELENA (Université de Bordeaux), Bordeaux

<sup>4</sup>IMS (Université de Bordeaux) et GIP-CNFM, Bordeaux

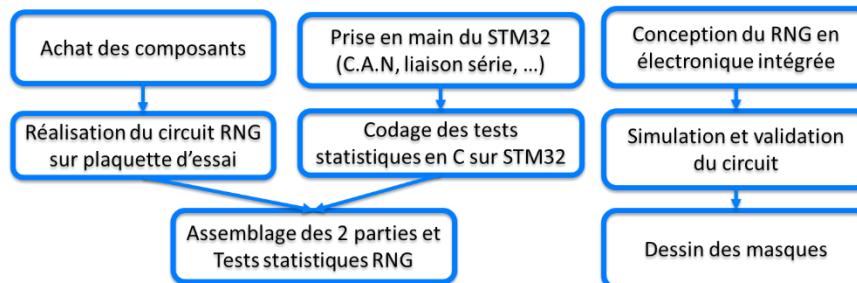

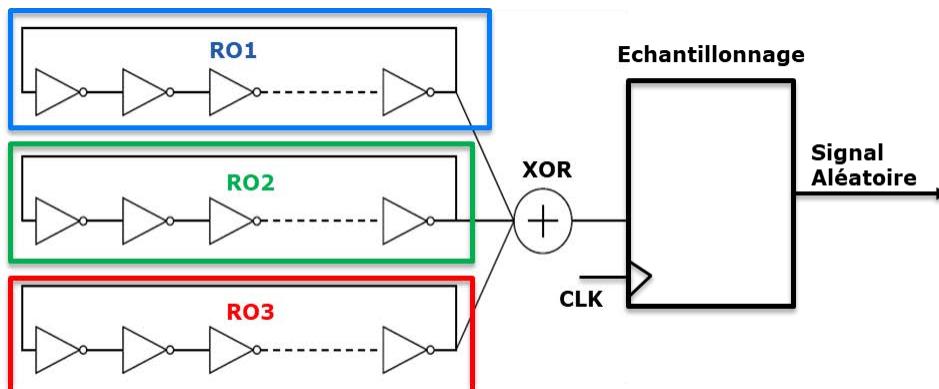

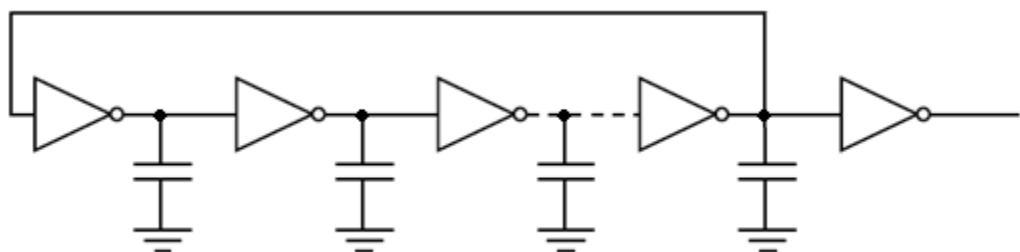

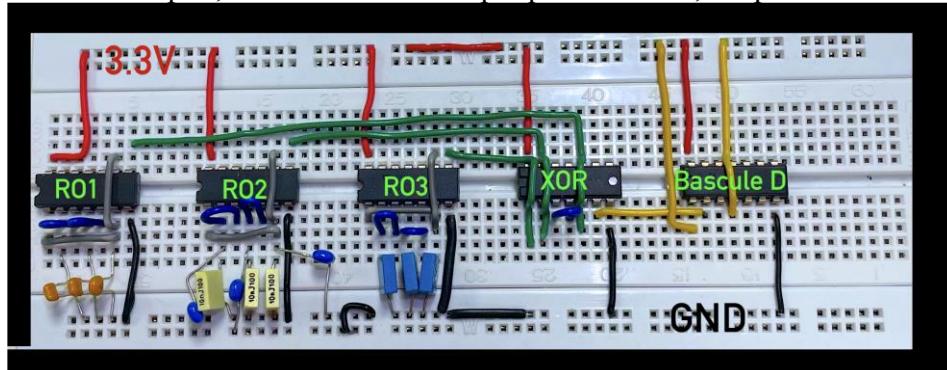

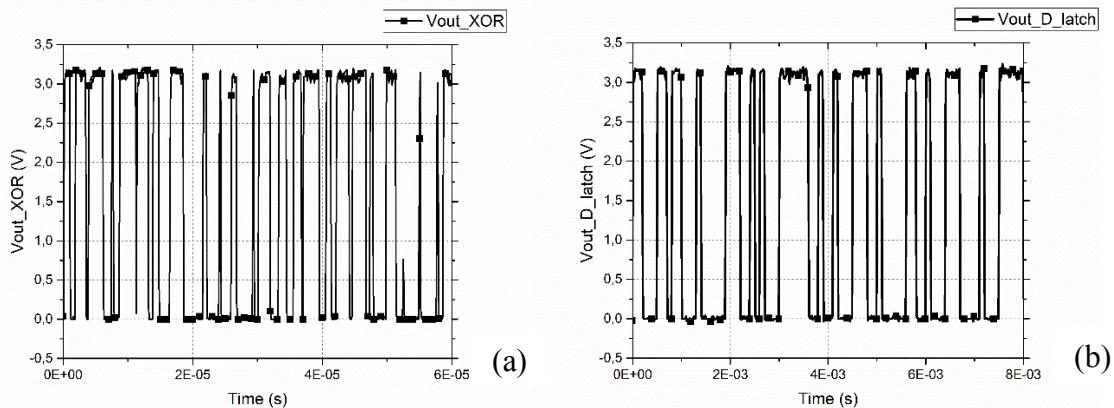

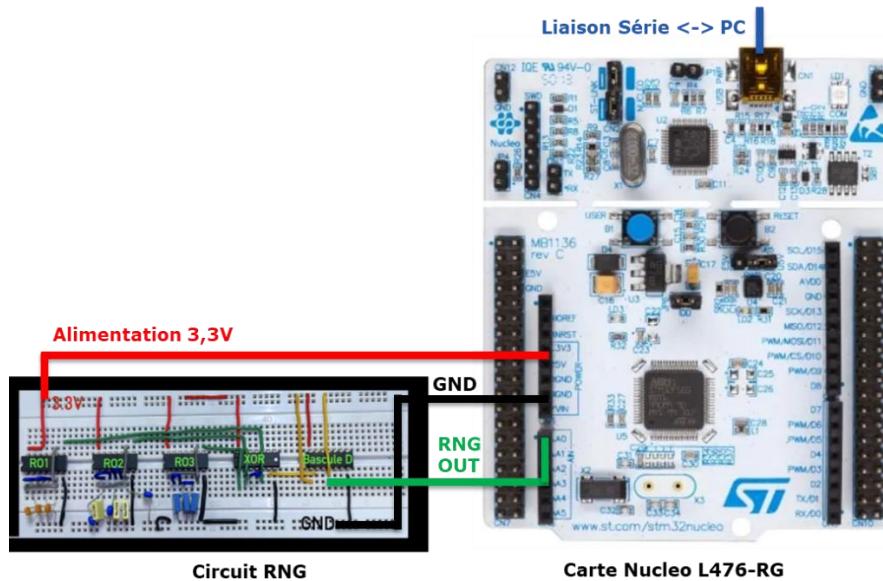

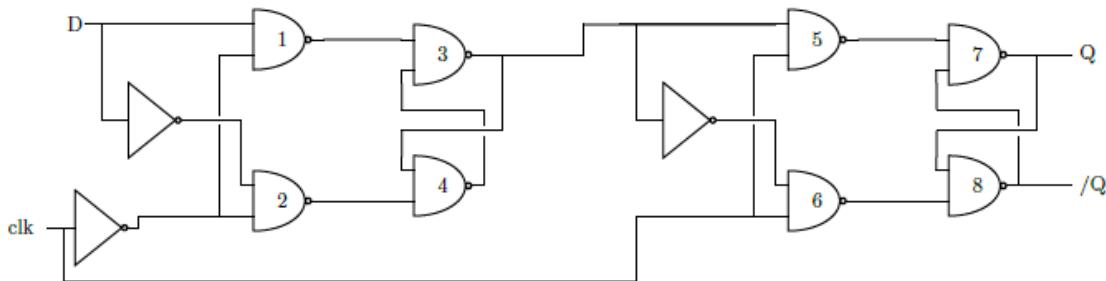

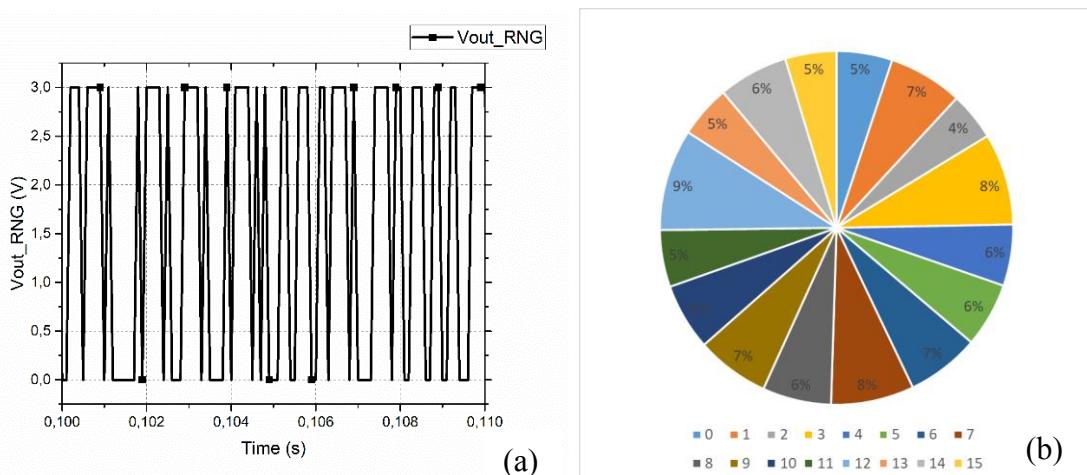

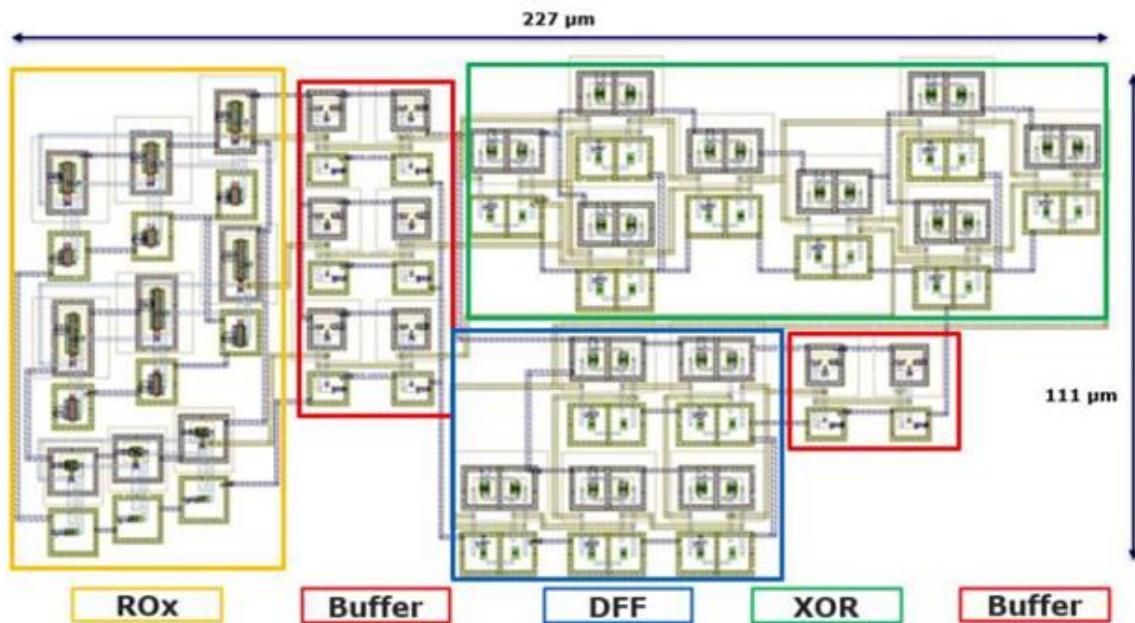

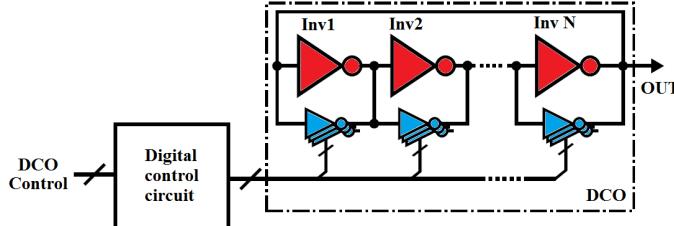

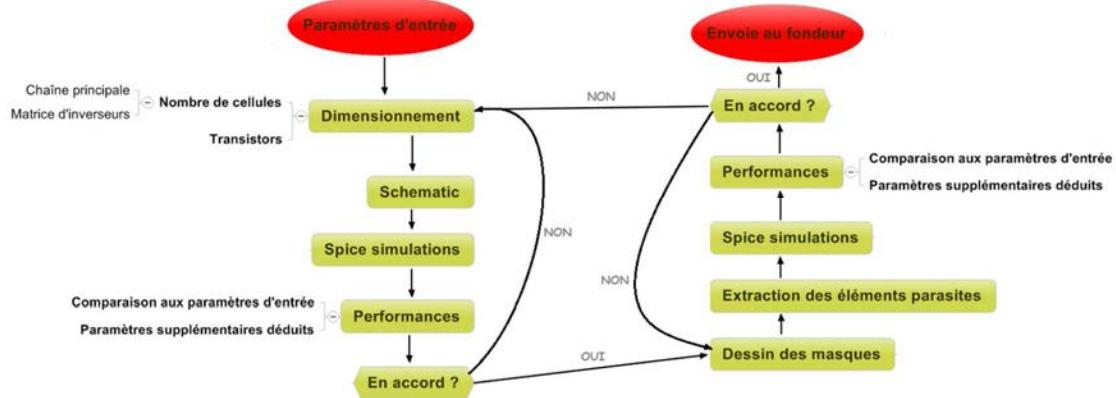

**17 h 05 Conception d'un générateur de nombre aléatoire**

P28

M. Guérin, S. Meillère, P. Pannier, J. Postel-Pellerin, R. Laffont

Polytech Marseille, Technopôle de Château-Gombert, Marseille

PACA

**17 h 10 PAUSE - DÉMONSTRATIONS - POSTERS**

**Nouveaux outils – nouvelles formations**

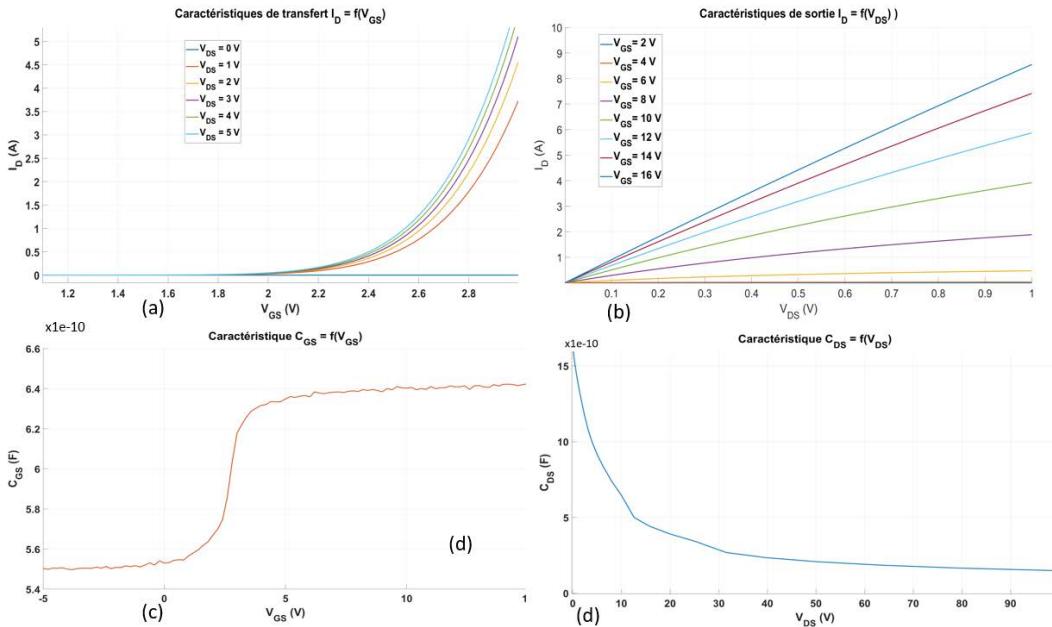

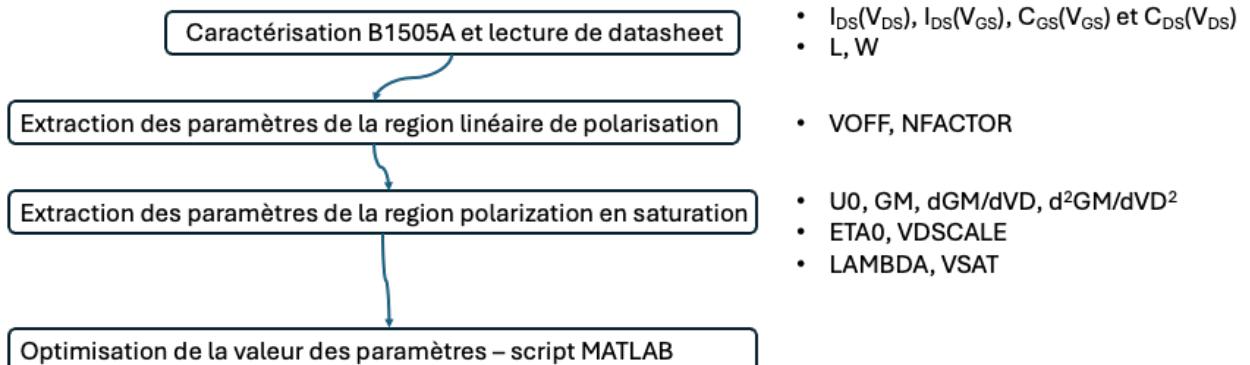

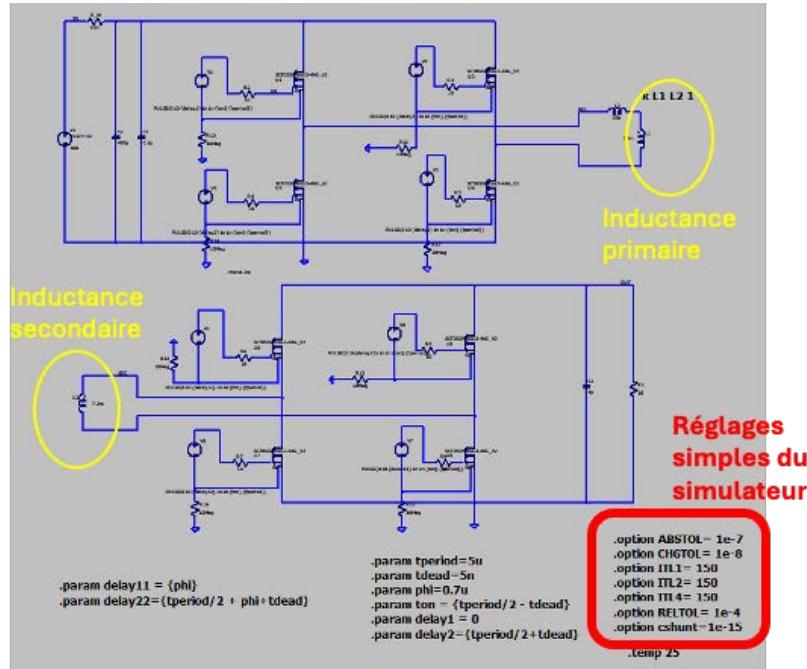

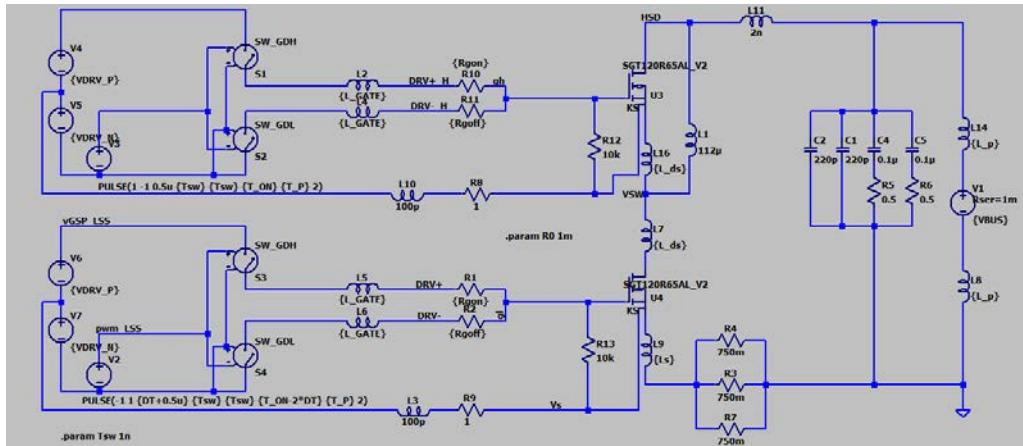

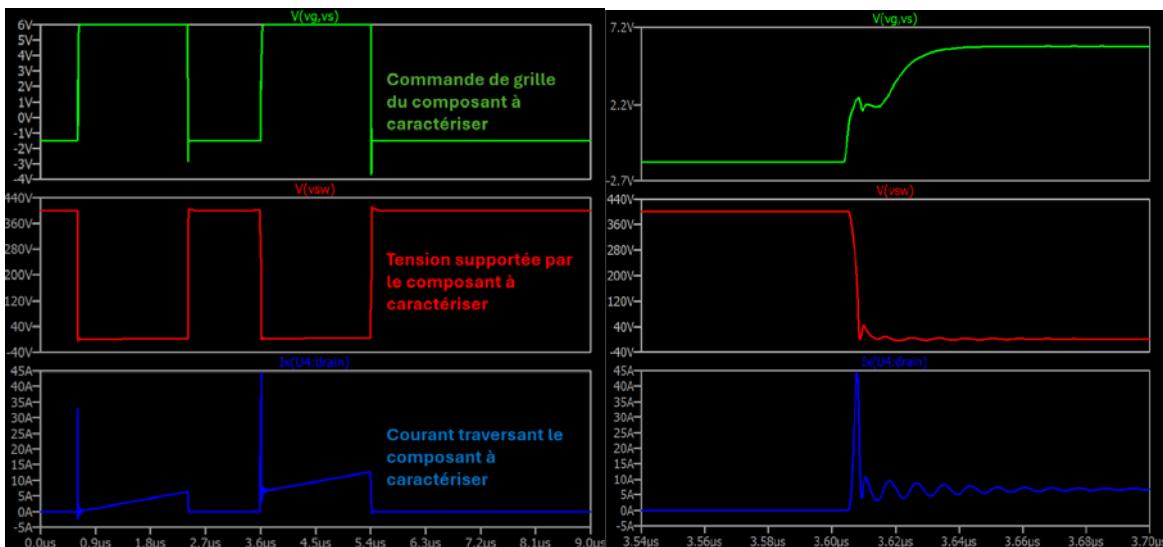

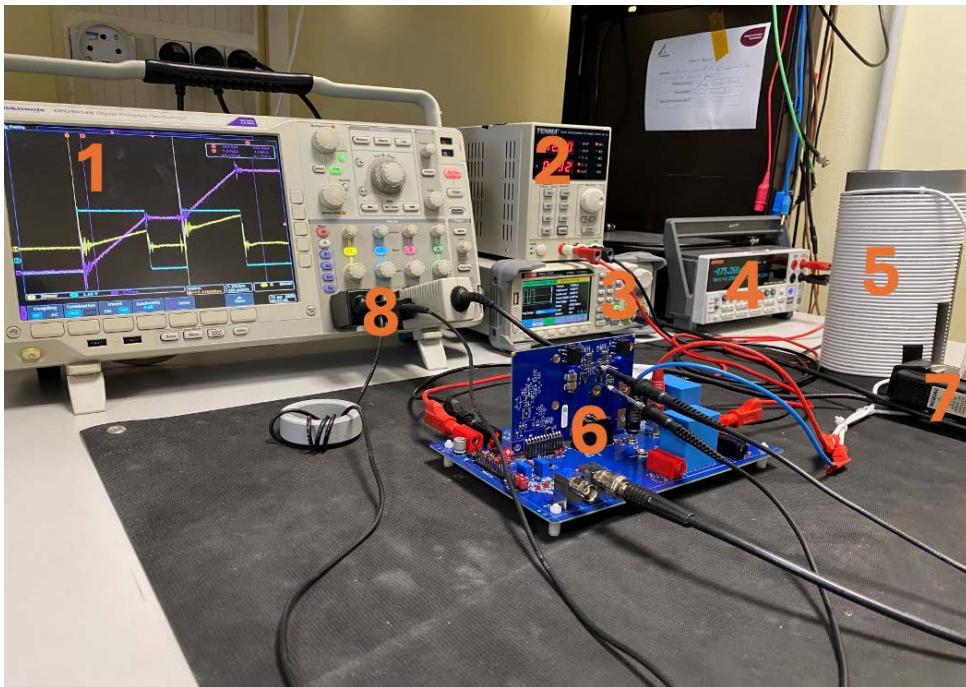

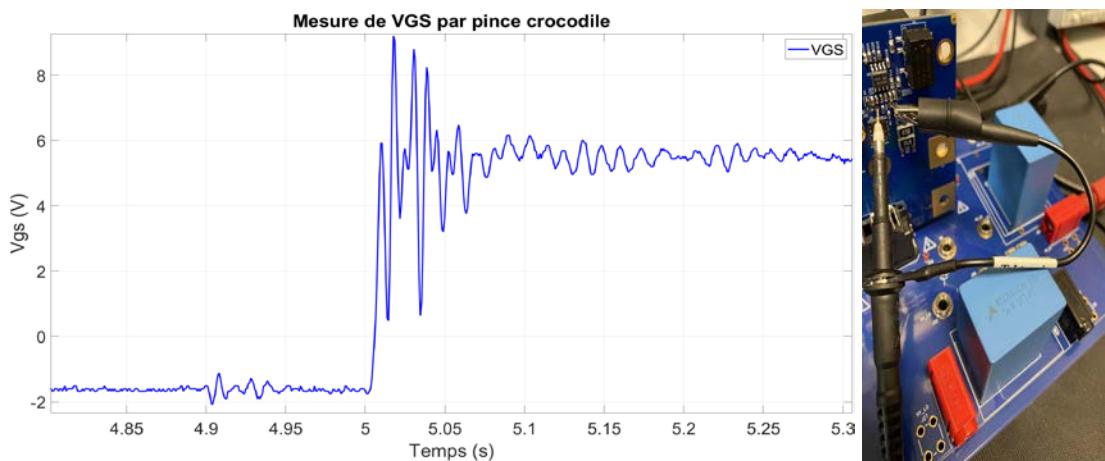

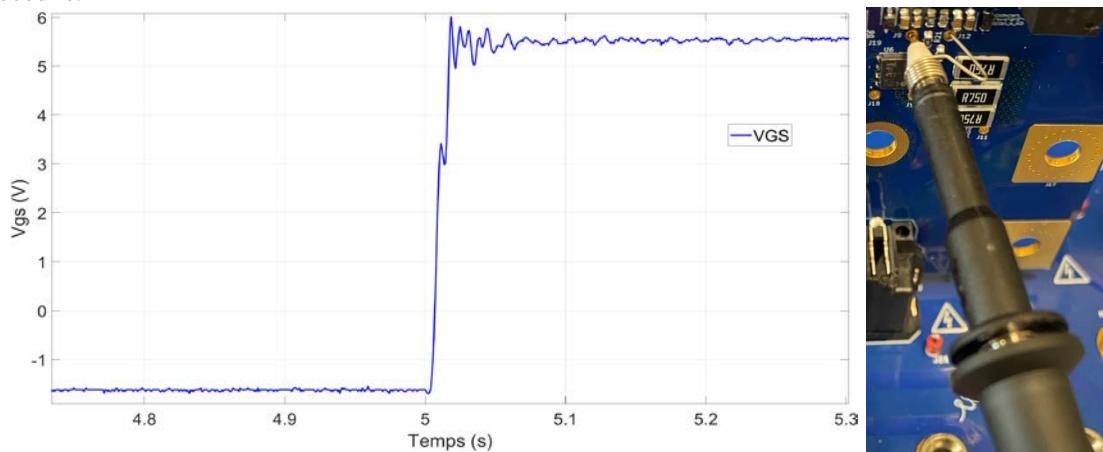

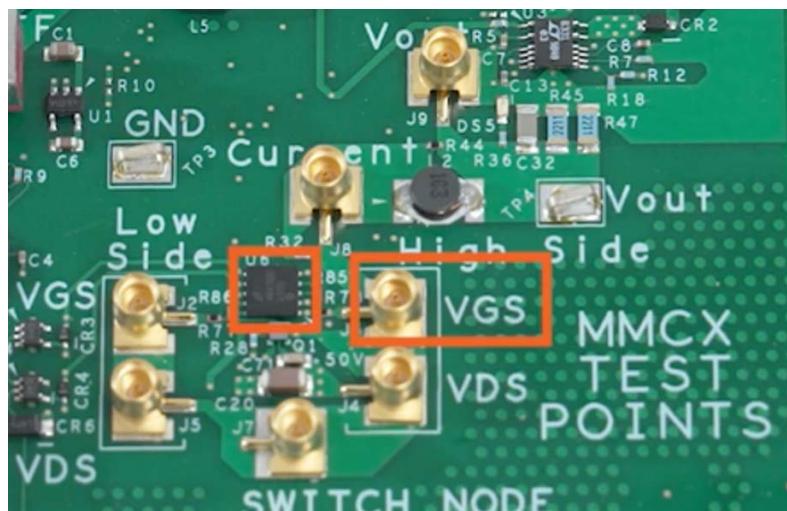

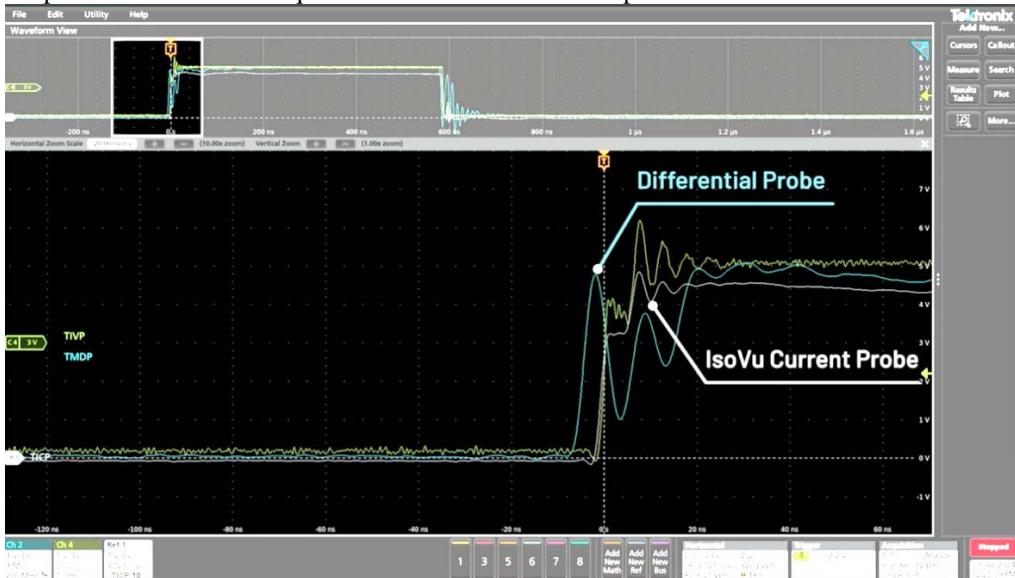

**17 h 40 De la caractérisation à la construction de modèles de composants de puissance à semiconducteur à grand gap**

P23a

B. Niass Ndao, P. Brosselard, B. Allard

Ampère, INSA Lyon, Villeurbanne

CIMIRLY

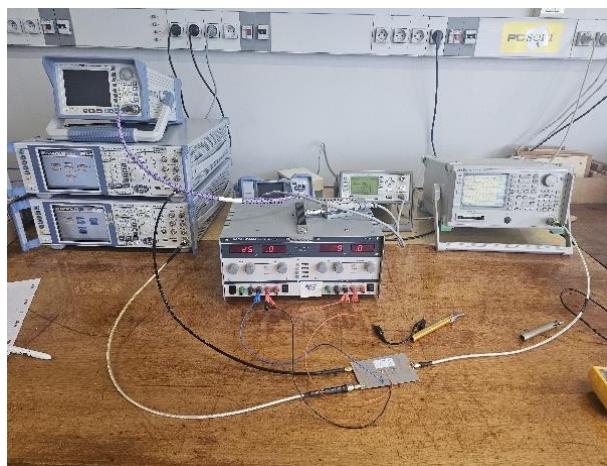

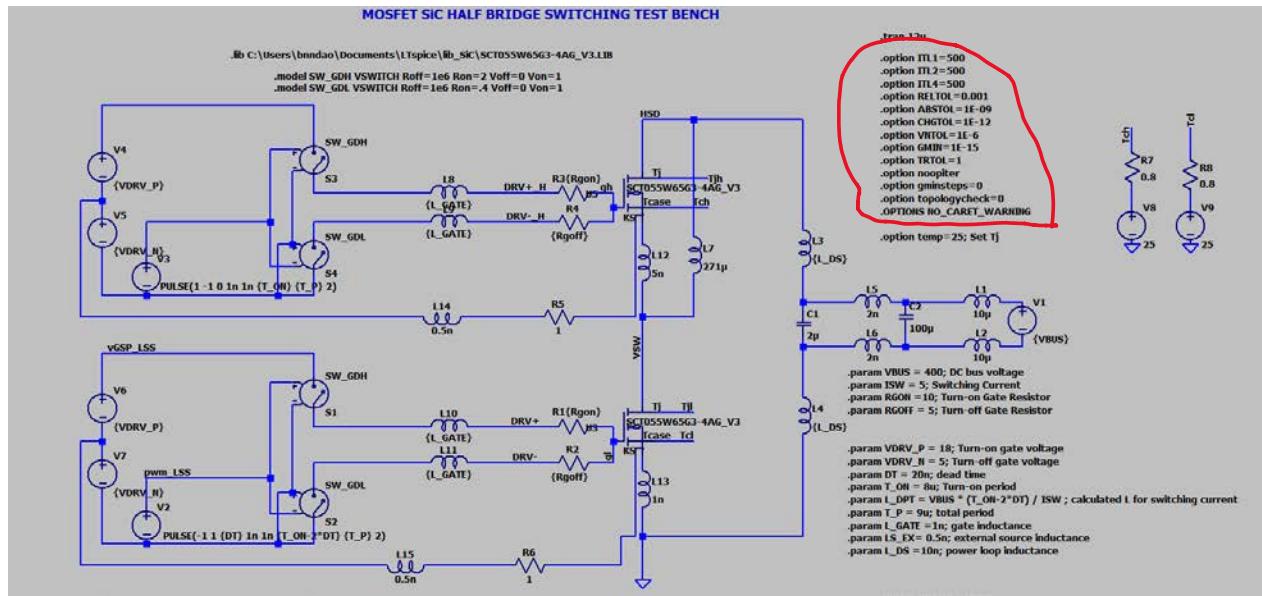

**17 h 45 Banc Double-Impulsions pour la caractérisation de composants de semiconducteur puissance à grand-gap**

P23b

B. Niass Ndao, P. Brosselard, B. Allard

Ampère, INSA Lyon, Villeurbanne

CIMIRLY

|                                                                                                                                                                                                             |                                                                                                                                    |         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------|

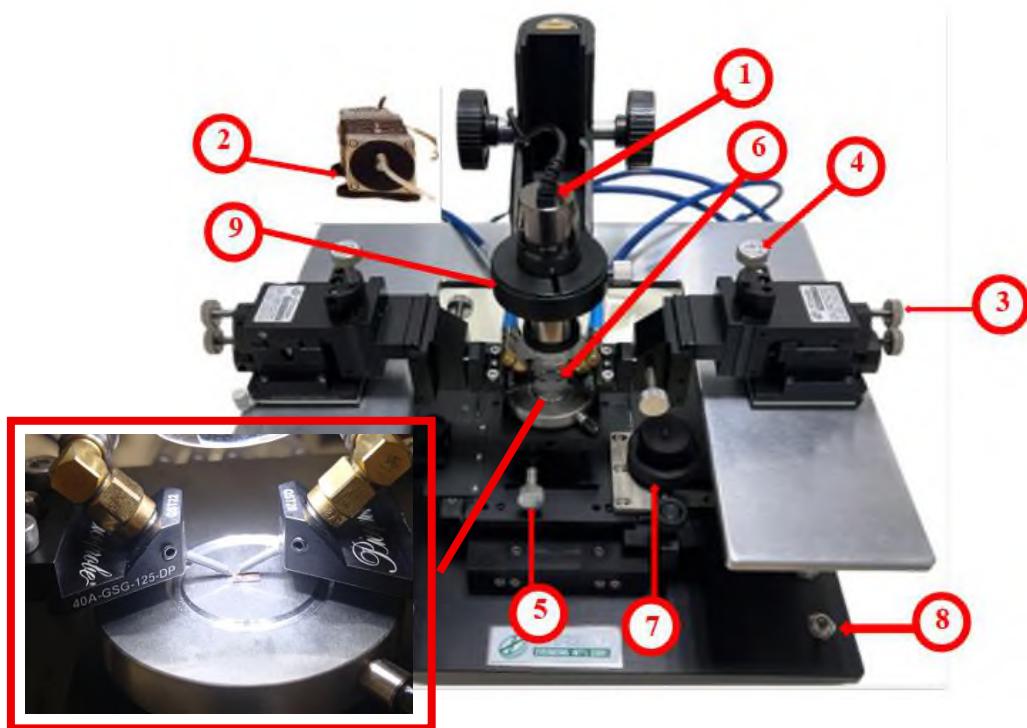

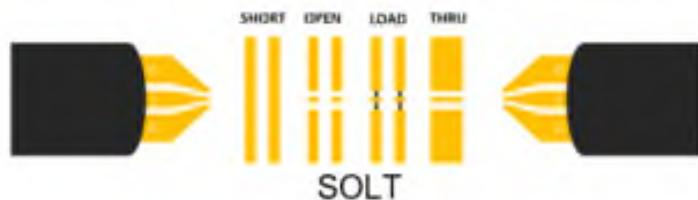

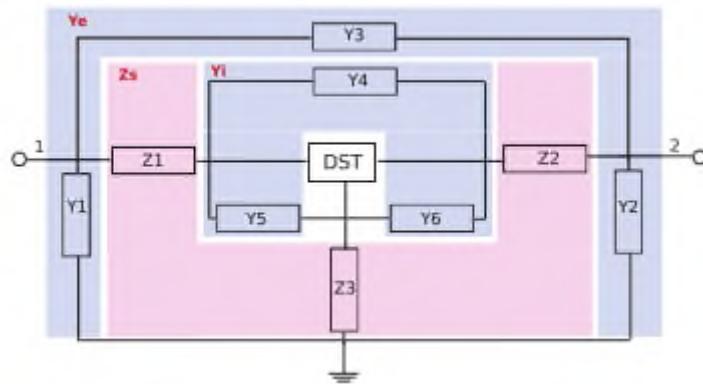

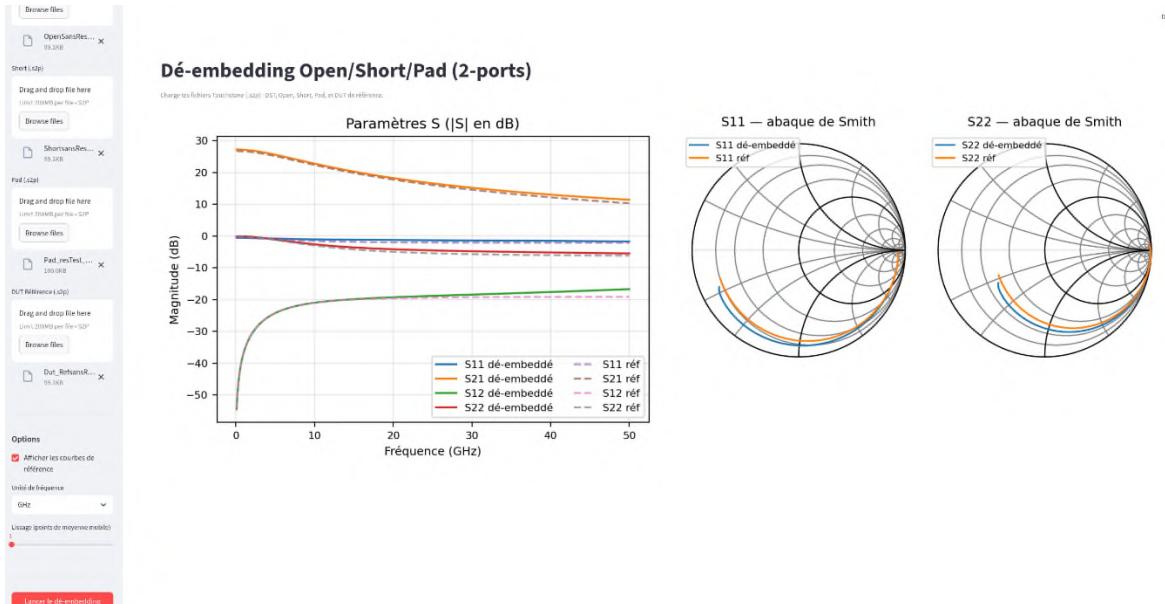

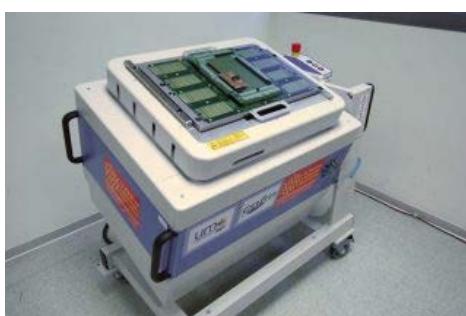

| <b>17 h 50</b>                                                                                                                                                                                              | Mise en œuvre d'une station sous pointes pour la caractérisation de composants intégrés silicium avec étalonnage de type SOLT      | P24     |

| K. Djebbar, D. Passerieux, B. Barelaud, O. Tantot, J. Lintignat<br><i>XLIM, UMR 7252, Université de Limoges/CNRS, 123 av A. Thomas, 87060 Limoges</i>                                                       |                                                                                                                                    | PLM     |

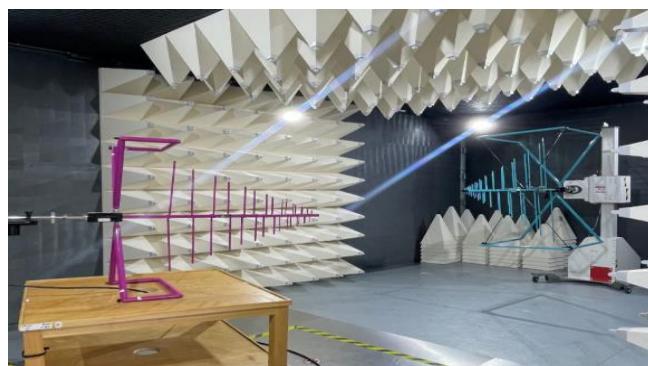

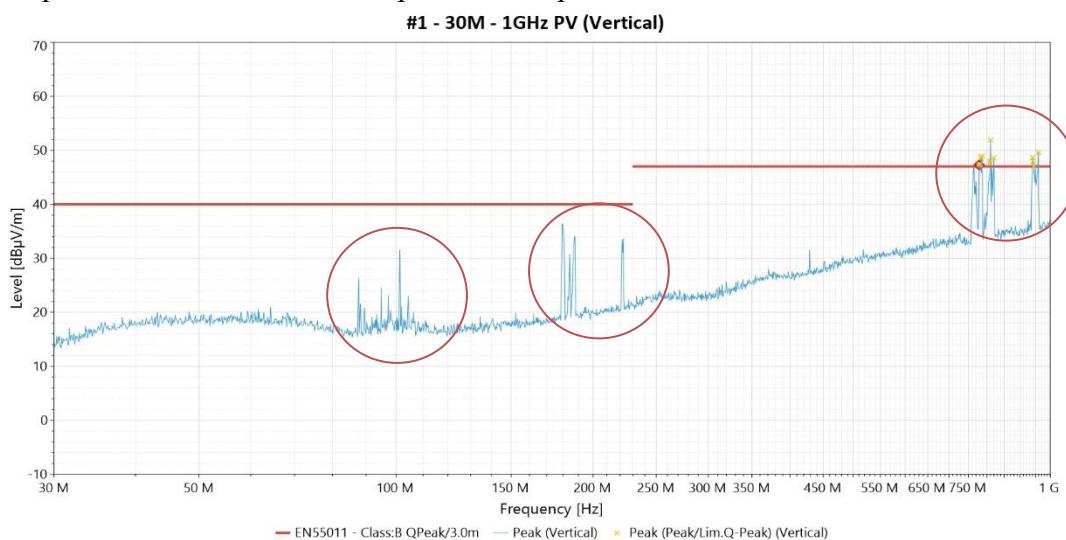

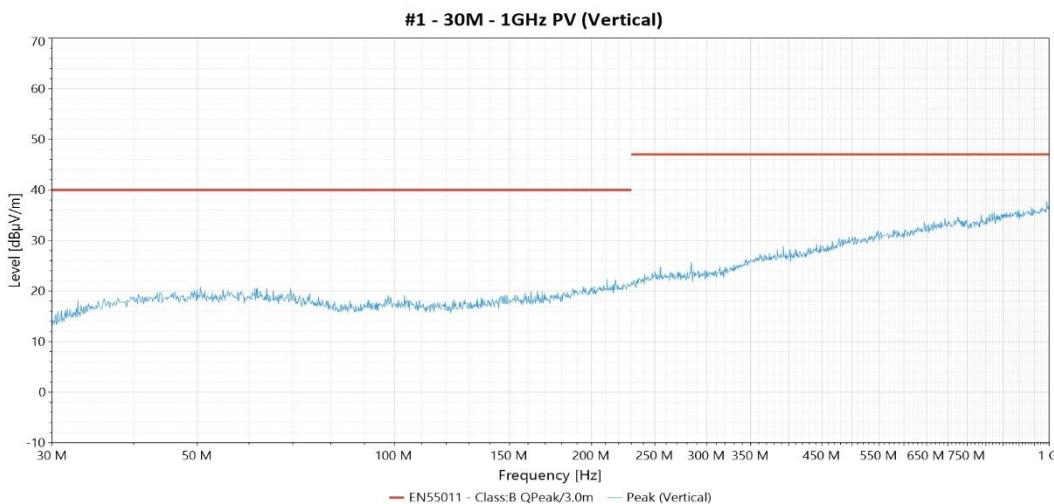

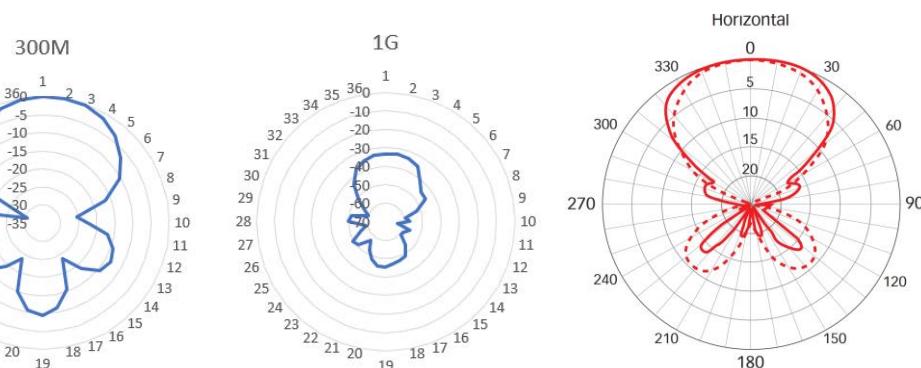

| <b>17 h 55</b>                                                                                                                                                                                              | <b>Essais CEM en cage de Faraday</b>                                                                                               | P25     |

| <sup>1,2</sup> D. Sleiman, <sup>1,2</sup> W. Uhring, <sup>1</sup> N. Collin<br><sup>1</sup> ICube Université de Strasbourg, Strasbourg<br><sup>2</sup> IUT de Haguenau (Université de Strasbourg), Haguenau |                                                                                                                                    | MIGREST |

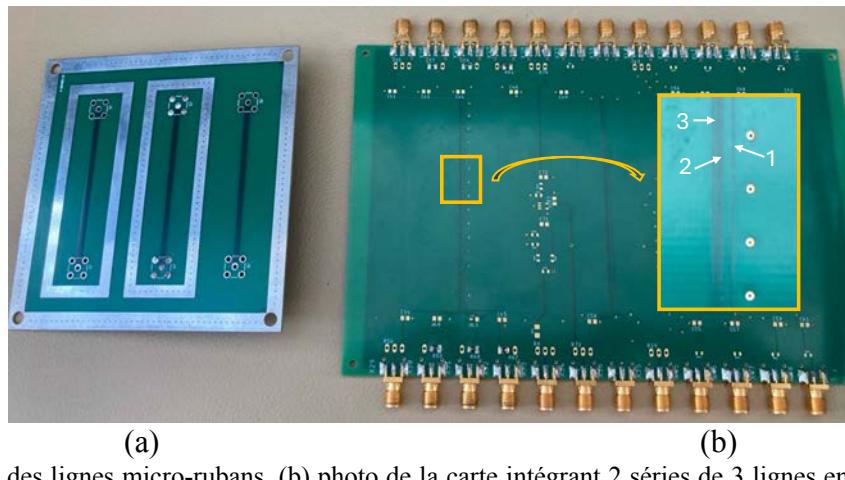

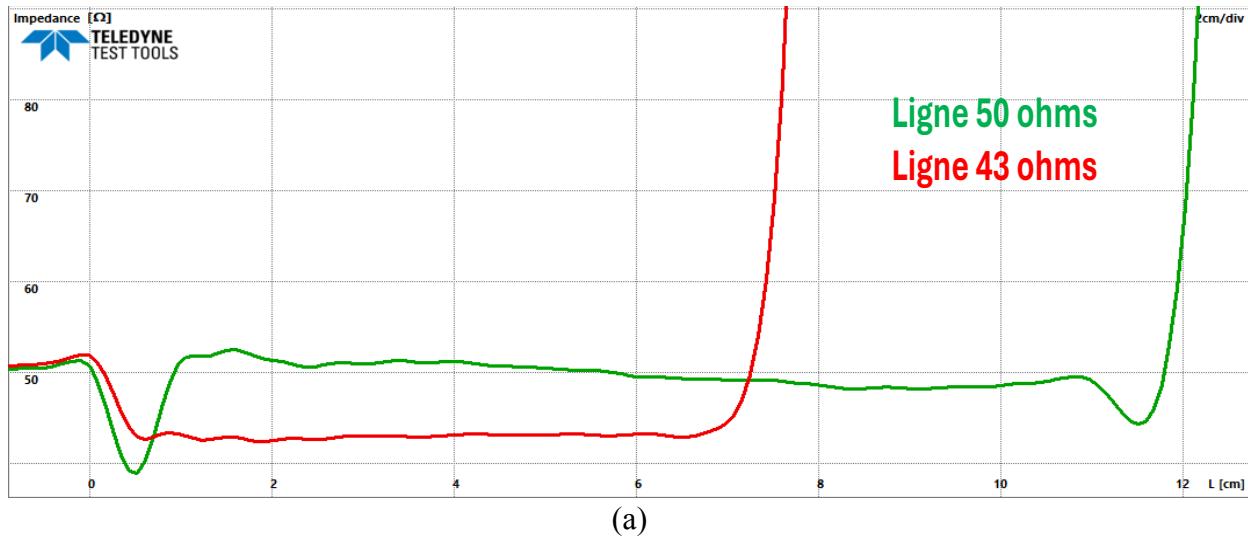

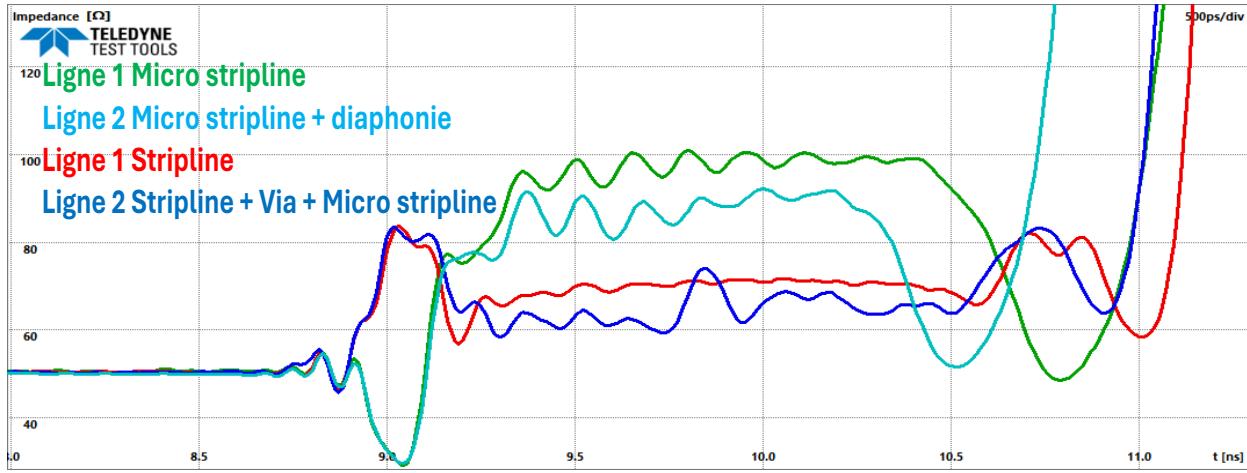

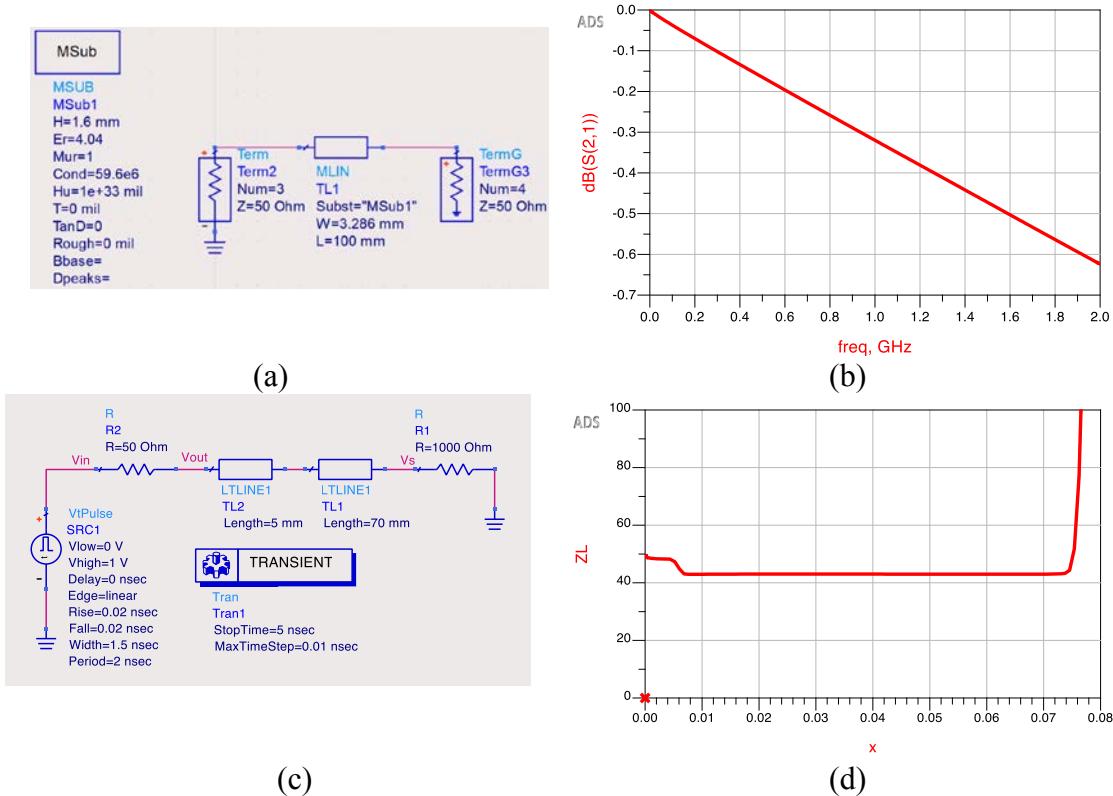

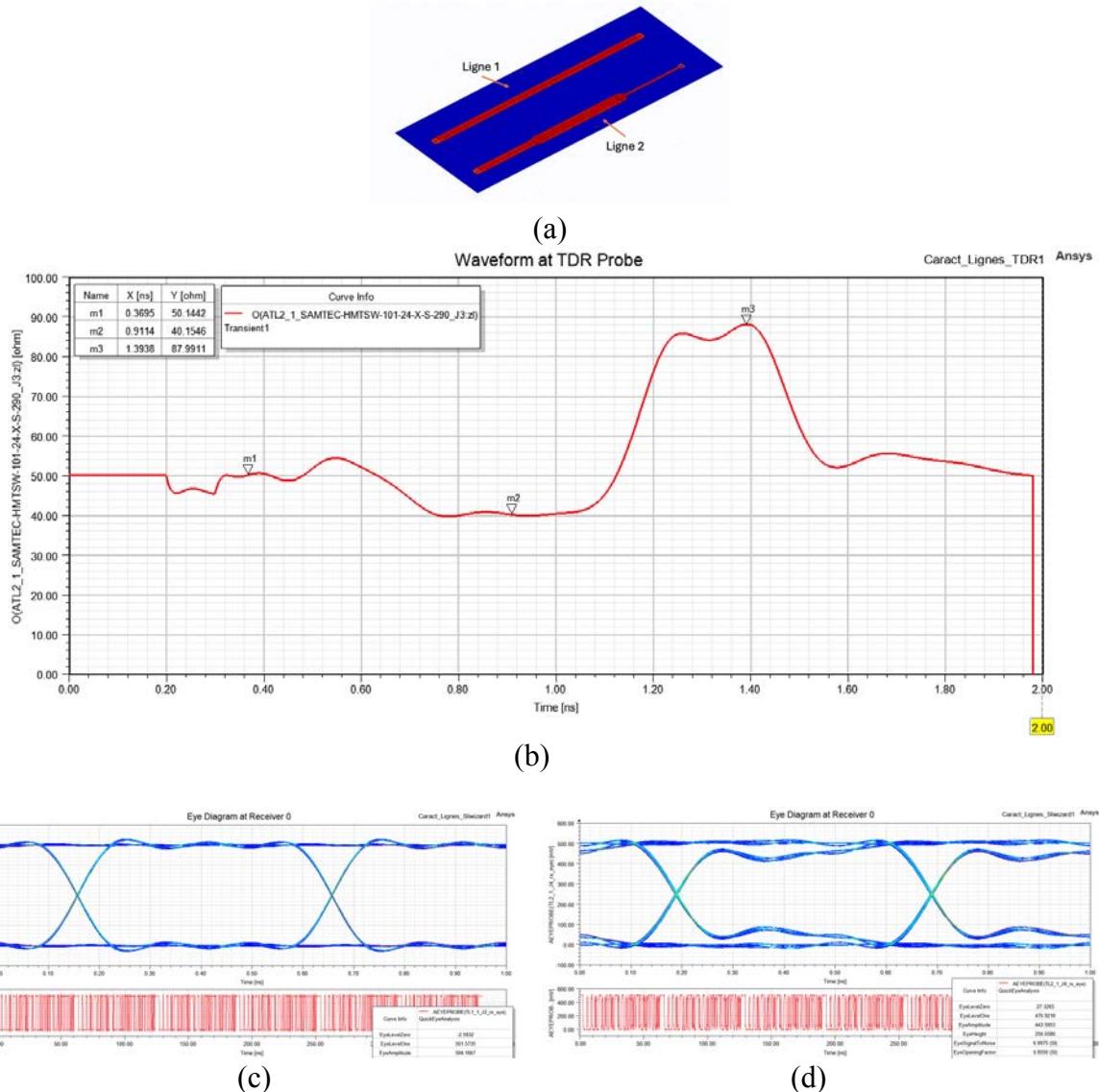

| <b>18 h 00</b>                                                                                                                                                                                              | <b>Étudier l'intégrité du signal dans les PCBs : expérimentation et modélisation</b>                                               | P26     |

| T. Dubois, R. Boni Salifou, A. Duguet, G. Costa e Silva, S. Le Bihan<br><i>IMS, Université de Bordeaux, Bordeaux, France</i>                                                                                |                                                                                                                                    | PCB     |

| <b>18 h 05</b>                                                                                                                                                                                              | <b>International Summer School on Micro and Nano-fabrication tools for innovating applied electronics and fundamental research</b> | P27a    |

| R. Tan, J. Harmel, C. Capello, C. Rouabhi, J. Schäuber, H. Azeroual, I. Konate, J. B. Lincelles, M. Mauguet, X. Marie, M. Respaud<br><i>AIME, Toulouse</i>                                                  |                                                                                                                                    | AIME    |

| <b>18 h 10</b>                                                                                                                                                                                              | <b>Les technologies quantiques appliquées pour les capteurs à forte sensibilité et communication sécurisés</b>                     | P27b    |

| Maxime Mauguet, André Ballochi, Cédric Robert, Thomas Boulier, Xavier Marie, M. Respaud<br><i>AIME, Toulouse</i>                                                                                            |                                                                                                                                    | AIME    |

### Actions CSF

|                                                                                                                                                                                        |                                                                                          |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----|

| <b>18 h 15</b>                                                                                                                                                                         | <b>Les actions du CSF électronique pour l'emploi et le développement des compétences</b> | 09 |

| <sup>1</sup> S. Beaufils, <sup>2,1</sup> V. Hoël<br><sup>1</sup> CSF Electronique – GT emploi formation compétences<br><sup>2</sup> PLFM Pôle CNFM Lille et GIP-CNFM, Grenoble, France |                                                                                          |    |

### 18 h 40 DÉMONSTRATIONS – POSTERS (Suite)

### 20 h 00 DÎNER

**VENDREDI 5 DECEMBRE 2025**

**Projets AMI-CMA**

|               |                                                                                                                                      |     |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>9 h 00</b> | <b>Présentation du projet AMI-CMA CAP ELENA</b><br>S. Hémour<br><i>IMS, IUT Bordeaux, dpt GEII, Université de Bordeaux, Bordeaux</i> | O10 |

| <b>9 h 15</b> | <b>Présentation du projet AMI-CMA ESOS</b><br>V. Harel<br><i>INSA Rennes</i>                                                         | O11 |

**Conception**

|               |                                                                                                                                                                                                                                                                    |                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

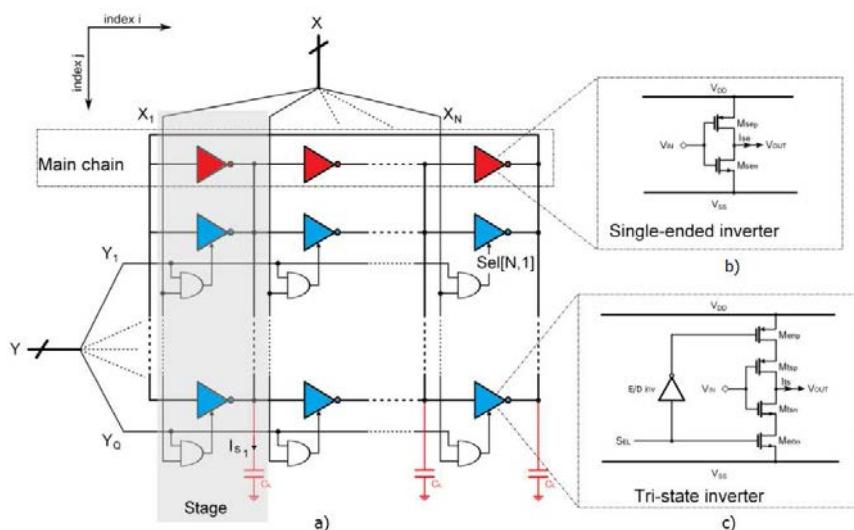

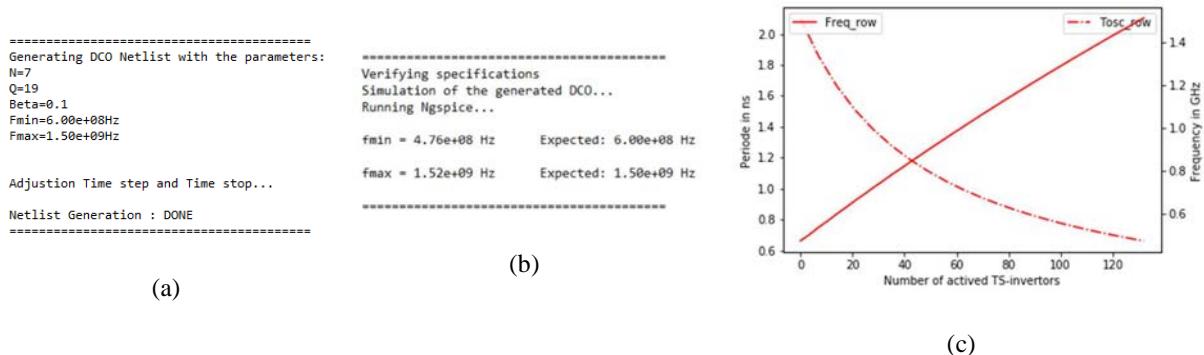

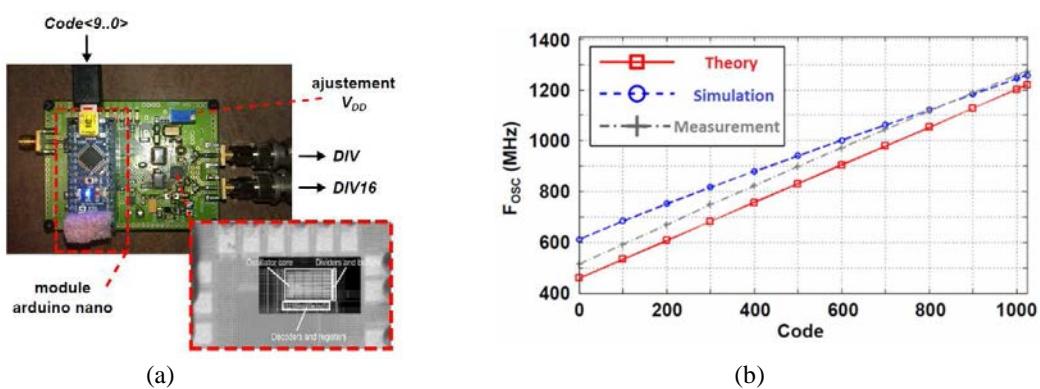

| <b>9 h 30</b> | <b>Conception automatisée d'oscillateurs configurables pour les systèmes sur puce : bilan d'un projet collaboratif et pédagogique</b><br>S. Feruglio, D. Galayko, F. Vallette, J-P. Chaput, M-M. Louérat<br><i>LIP6, CNRS UMR 7606, Sorbonne Université, Paris</i> | P29<br><br>CEMIP   |

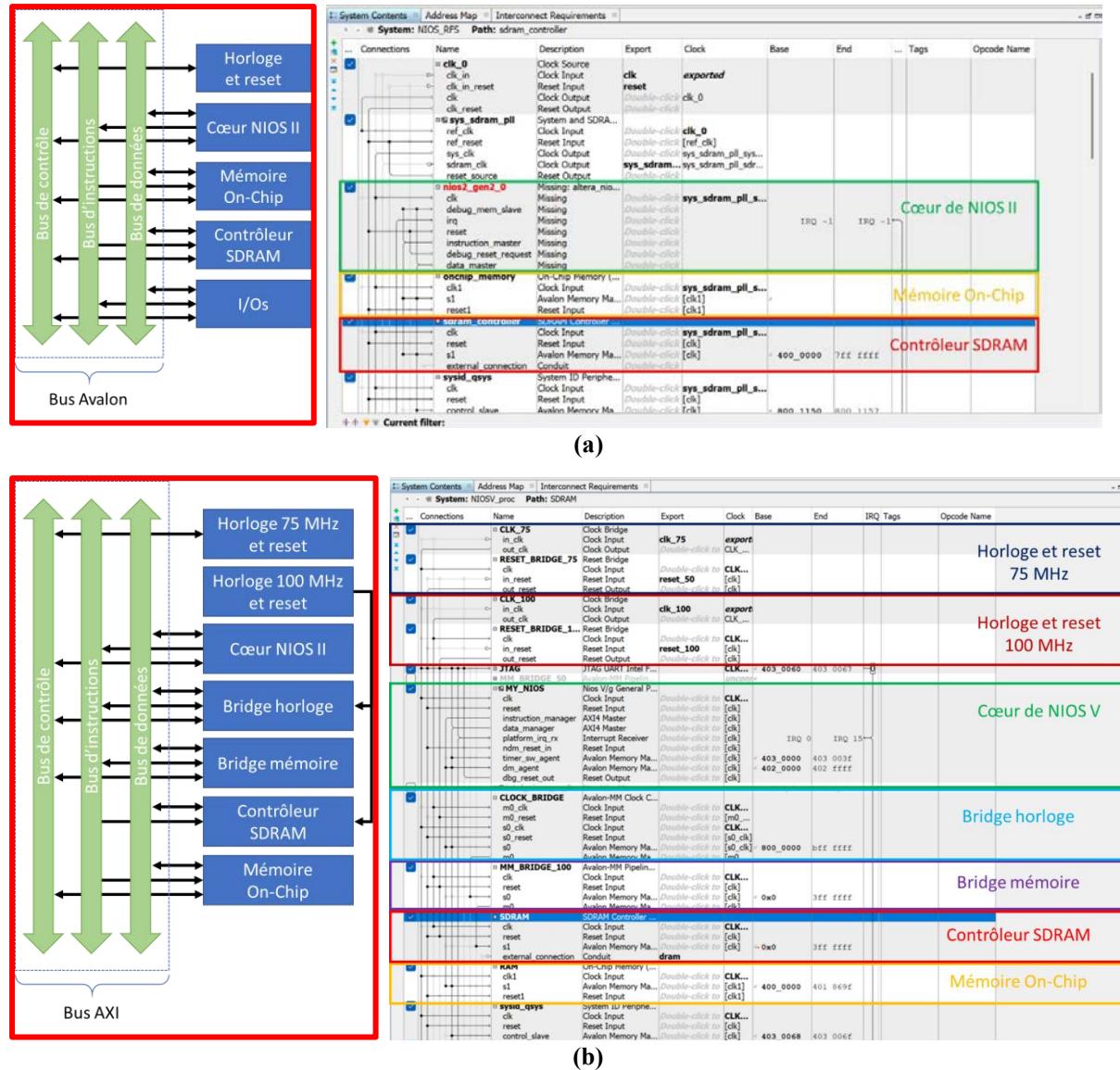

| <b>9 h 35</b> | <b>Migration NIOS II vers NIOS V sur carte DE10-Lite : un levier technique et pédagogique pour l'enseignement des systèmes embarqués.</b><br>V. Frick<br><i>ICube, Université de Strasbourg, Strasbourg</i>                                                        | P30<br><br>MIGREST |

| <b>9 h 40</b> | <b>Introduction à la Conception FPGA en Master 1</b><br>W. Pensac<br><i>Polytech Montpellier, LIRMM CNRS 5506, Université de Montpellier, Montpellier</i>                                                                                                          | P31<br><br>PCM     |

**Attractivité**

|               |                                                                                                                                                                                                                                                                                                                                                                 |                  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

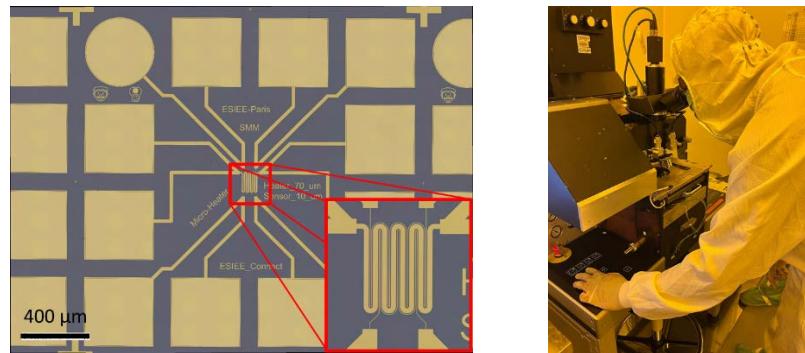

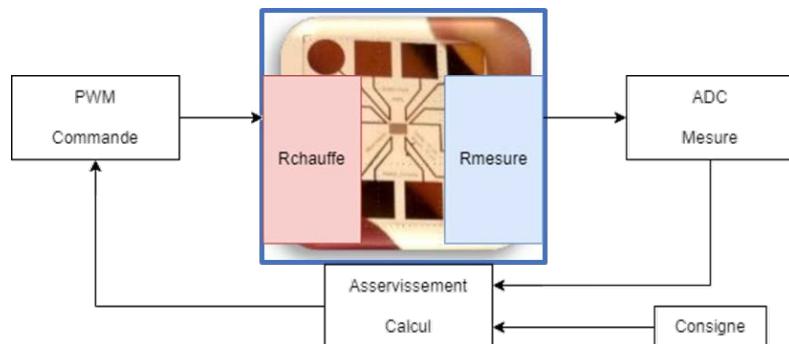

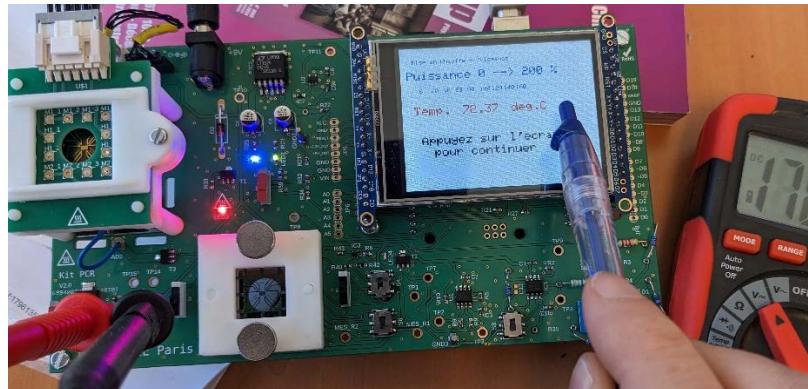

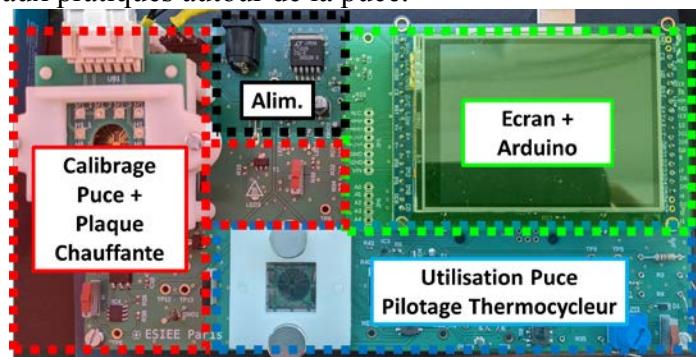

| <b>9 h 45</b> | <b>Kit pédagogique pour la sensibilisation aux métiers de la micro-électronique</b><br>¹O.François, ¹L. Rousseau, ¹P. Poulichet, ¹J. Pagazani, ¹N. Pavy,<br>¹N. Ben Moussa, ²P. Auvray<br><i>¹ESIEE Paris, Université Gustave Eiffel, Noisy Le Grand<br/>²Mindyllis, Caen</i>                                                                                   | P33<br><br>CEMIP |

| <b>9 h 50</b> | <b>Effets musicaux et circuits électroniques : une pédagogie active pour l'enseignement de l'électronique</b><br>R. Mohellebi, D.-K.G. Pham, K. Ben Kalaia, C. Jabbour<br><i>Equipe C2S, LTCI, Télécom Paris, Institut Polytechnique de Paris, Palaiseau</i>                                                                                                    | P34<br><br>CEMIP |

| <b>9 h 55</b> | <b>Attractivité de l'électronique : des mallettes connectées pour les collégiens</b><br>¹S. Avrillon, ²G. Debert, ²O. Demiraslan, ²S. Druart, ²D. Evellin, ³L. Boursier,<br>³A. Coquet, ³G. Griffon, ³M. Nouvel, ³T. Poitevineau<br><i>¹IETR, Université de Rennes, Rennes<br/>²Enseignants de l'Académie de Rennes<br/>³Elèves apprentis de l'ESIR, Rennes</i> | P35<br><br>CCMO  |

**10 h 00 PAUSE - DÉMONSTRATIONS - POSTERS**

|              |                                                                                            |     |

|--------------|--------------------------------------------------------------------------------------------|-----|

| <b>10:45</b> | <b>Présentation projet AMI-CMA INFORISM</b><br>O. Bonnaud - DG GIP-CNFM                    | O12 |

| <b>10:55</b> | <b>Présentation projet AMI-CMA ASTEERICS-C2FM</b><br>O. Bonnaud DG GIP-CNFM                | O13 |

| <b>11:05</b> | <b>Echange sur les actions Attractivités futures des AMI-CMA</b><br>O. Bonnaud DG GIP-CNFM | T3  |

| <b>11:15</b> | <b>CLOTURE DES JPCNFM 2025</b><br>O. Bonnaud , J.L. Estienne, A-C. Salaün et L. Pichon     |     |

**12 h 00 DÉJEUNER**

**14 h 00 FIN DES JOURNEES**

# Fabrication de circuits intégrés durant des programmes doctoraux en technologie GaN et en 65nm : une accélération d'innovations

L. Trojman<sup>a</sup>, E. Holguin<sup>b</sup>, N. Pozo<sup>b</sup>, K. Vicuna<sup>a,c</sup>, L.-M. Procel<sup>b</sup>, F. Crupi<sup>c</sup>, F. Amiel<sup>a</sup>

<sup>a</sup>LISITE, Isep, Issy-Les-Moulineaux, France

<sup>b</sup> Université San Francisco de Quito (USFQ), Quito, Equateur

<sup>c</sup>Université de Calabres, UNICAL, Rende, Italie

Contact email : [lionel.trojman@isep.fr](mailto:lionel.trojman@isep.fr)

Dans un contexte où la micro et nanoélectronique reprend une position prédominante sur la scène internationale, nous avons dans notre laboratoire, le LISITE en collaboration avec nos partenaires de l'UNICAL et de l'USFQ dédié des programmes doctoraux dans des champs d'application innovant. Nous avons développé en électronique puissance en développant entre autres le concept de System-on-Chip de puissance en technologie GaN. Et sur les thèmes de la cryptographie exploité le concept des PUF en les rendant accessibles dans n'importe quel FPGA sans sacrifier sa performance. 80% de ces projets ont conduit à la fabrication d'un circuit intégré soit en technologie 180nm, 65nm ou p-GaN dans le cadre des programmes Europractice et Ascent+.

## I. Introduction

Les 5 dernières années ont été décisives pour les technologies micro et nanoélectronique. Tout d'abord la crise sanitaire du COVID19 a impulsé dans un large spectre des métiers et fonction sociales une utilisation accrue des outils numériques (1). Nous retrouvons essentiellement des applications reposant sur la digitalisation des contenus informatif (factuel et contextuelle) et leur stockage dans le cloud. Ensuite l'évènement de « l'IA générative » et sa diffusion au grand public en 2022 amenant à repenser le rapport entre les humains et les machines et soulevant par ailleurs beaucoup de question d'éthique (2).

Ces événements démontrent que les besoins en calcul vont continuer à croître pour rendre ces applications plus rentables pour l'industrie et mieux intégré aux sociétés humaines ; aujourd'hui NVIDIA montre un CA de \$5TnUSD (3) et TSMC prévoit la production du nœud A14 (1.4nm) pour 2028 (4). Les fournisseurs de solution IA se retrouvent aussi dans une situation de développement intense : Openai est devenu un organisme à but lucratif, Google et Microsoft veulent développer leur propre microprocesseur pour entraîner leur modèle d'AI (5). En parallèle l'industrie des semiconducteurs « devient » une technologie souveraine et cadence les enjeux géopolitique et géoéconomique de l'orient à l'occident autour de la nouvelle route la soie.

Face à cette nouvelle donne, des défis critique émergent, défis dont nous choisirons 2 plus spécifiquement. La stratégie énergétique pour alimenter ces systèmes est une question des plus critiques dans un contexte environnemental contraint par l'appauvrissement des ressources naturelle. Puis d'un autre côté, la digitalisation des informations et la virtualisation des systèmes soulèvent une question fondamentale sur la sécurité et la protection des données. A l'Isep dans notre laboratoire du LISITE nous nous sommes concentrés spécifiquement sur ces 2 axes pour développer nos projets de recherche sur ces 5 dernières années.

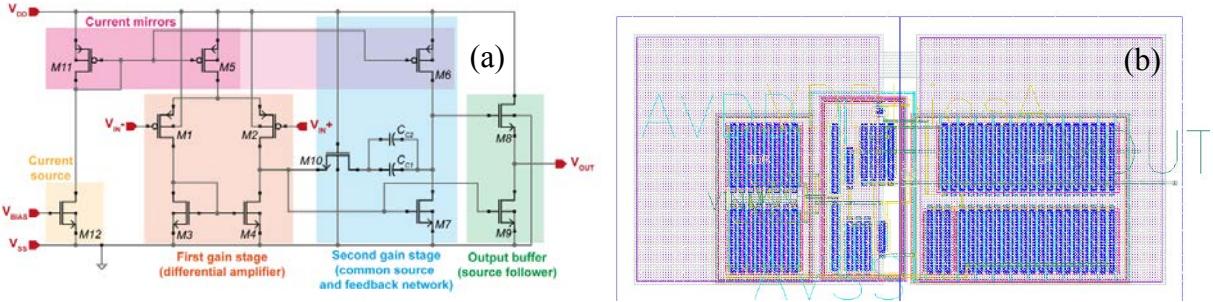

## I. Un Amplificateur Opérationnel frugal et performant en 180nm

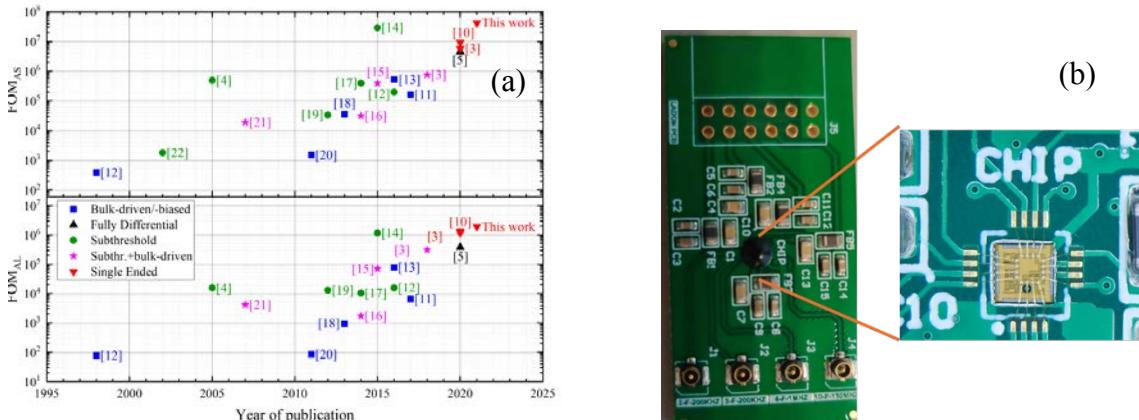

Un incontournable de l'électronique analogique trouvant des applications dans le conditionnement des signaux provenant des capteurs pour de la mesure physique ou dans la conversion analogique et digital. Ce qui le rend puissant en design c'est certainement la possibilité de « modular » ses performances le rendant à la fois versatile et indémodable. Aujourd'hui on le retrouvera autant dans les systèmes embarqués ou les objets connectés pour assurer la précision et donc la stabilité en réponse des circuits, considérant le bruit de fonctionnement. Les besoins en système chaque fois plus performant à moindre « coût » de silicium et d'énergie, à motiver ce travail. L'idée (Fig. 1.a) a été de repartir d'un étage différentiel « sortie simple » (PMOS, M1-M2) avec une charge active (NMOS, M3-M4) en sortie pour constituer la boucle de gain (près de 50dB). La polarisation est fournie par le transistor M12 contrôlé par le miroir de courant (M11-M5). Cet étage est suivi d'un amplificateur en source commune qui boost le gain et dont la stabilité en fréquence est assurée par le réseau de Miller Cc1 et Cc2 jusqu'à une bande passante unitaire de près de 70MHz avec une confortable marge de phase de 86°. La résistance de sortie est définie par un buffer M8-M9 qui tient compte d'une très bonne linéarité. Le tout est alimenté avec par une source de 1V (rail à rail). Le layout (Fig. 1.b) a été fait avec une librairie PDK 180nm avec Cadence Virtuoso. Les figures de mérite (Fig. 2a) montrent que cette proposition de design fait partie des meilleures solutions lors de sa publication en 2021 (6). Le circuit a été fabriqué en 180nm dans le cadre d'un programme IEEE et Europractice (Fig. 2.b). Le packaging a été fait à l'université de Bar-Ilan. Il est prévu de l'utiliser aujourd'hui dans un système complexe de TCAM en technologie STT-MRAM.

Fig.1. Schéma électrique de l'AOP avec les différents étages d'amplification (a) et le layout sous Cadence fait en utilisant une librairie PDK en 180nm de TSMC (b).

Fig.2. Figure de mérite pour petit (FOM<sub>AS</sub>) et large signaux (FOM<sub>AL</sub>) en (a) et le circuit fabriqué dans sa carte de test (packaging) et avec le wirebonding fait à l'université de Bar-Ilan (b).

## II. Gestion d'énergie en technologie GaN

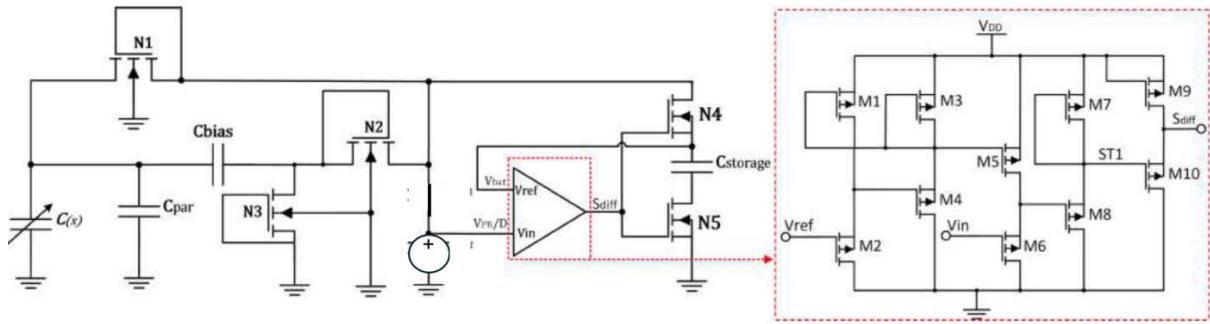

### A. Circuit de gestion de puissance en GaN pour un récupérateur d'énergie MEMS capacitif

Les récupérateurs d'énergie ont un rendement qui dépend nettement de l'unité de gestion de puissance et de la charge de sortie. Dans le cas d'un récupérateur de type MEMS capacitif à fermeture de gap, le circuit mobilise une très grande quantité de charges provoquant des tensions de l'ordre de 45V (7-8). Dans de tels conditions, une technologie silicium conventionnelle n'est plus aussi performante d'où notre choix de se tourner vers une technologie GaN qui supporte des tensions plus élevées (état OFF) pour une dissipation énergétique plus basse (état ON) (9). Le circuit de gestion de puissance que nous considérons (Fig. 3) comprend un système de pompe de charge pour une conversion AC-DC suivi d'un comparateur basse puissance pour détecter les niveaux de tension en excès. Une fois activé le comparateur conduit et dirige les charges récupérées dans le condensateur d'accumulation. Le niveau de tension de référence du comparateur (VPR/D) est fixé par une tension externe fixée de façon proportionnelle à la tension de rectification.

Fig.3. Schéma électrique de l'unité de gestion de puissance du MEMS capacitif. Ce dernier est représenté comme un condensateur variable avec la distance du gap. Le comparateur est explicité dans l'encadré en rouge où  $V_{in}$  = VPR/D propositionnel à la tension de rectification.

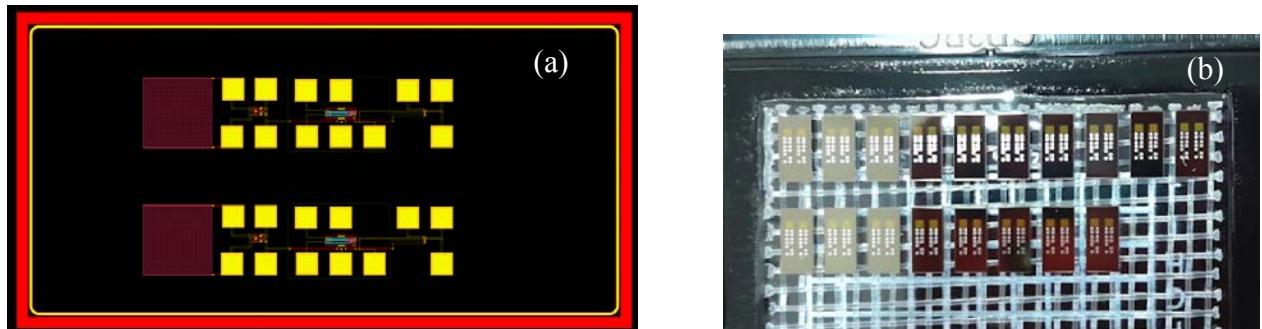

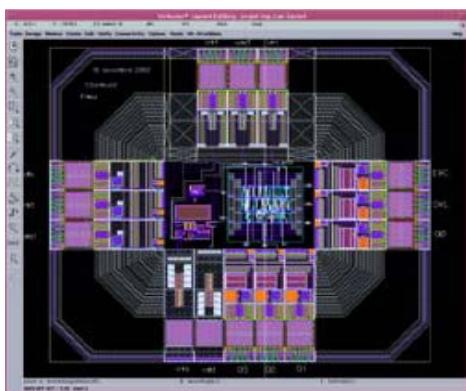

Le layout (Fig. 4.a) a été désigné en technologie p-GaN 200V provenant d'une librairie développée par Imec (10) en utilisant Cadence Virtuoso. Cette librairie à la particularité de proposer des HEMT en état normal OFF (dont la tension de seuil est positive). Cela nous a obligé à adapté le design du comparateur (Fig. 3, encadré rouge). Le circuit a été fabriqué dans le cadre du programme ASCENT+ (Fig. 4.b). L'inspection optique des échantillons montre un recouvrement complet par la couche de métal et un alignement correct de Pad avec un transfère précis de toutes les couches géométriques. Chaque die inclus 2 canaux indépendants pour les récupérateurs d'énergie de type MEMS. Les tests sous pointes sont en cours.

Fig.4. Layout du circuit de management puissance en (a) qui comprend 2 canaux indépendants et un pad pour la connexion au MEMS. Les échantillons des circuits fabriqués en GaN en (b).

## B. « System on Chip » (SoC) de puissance à base de technologie GaN avec un design restreint à des HEMT en E-mode

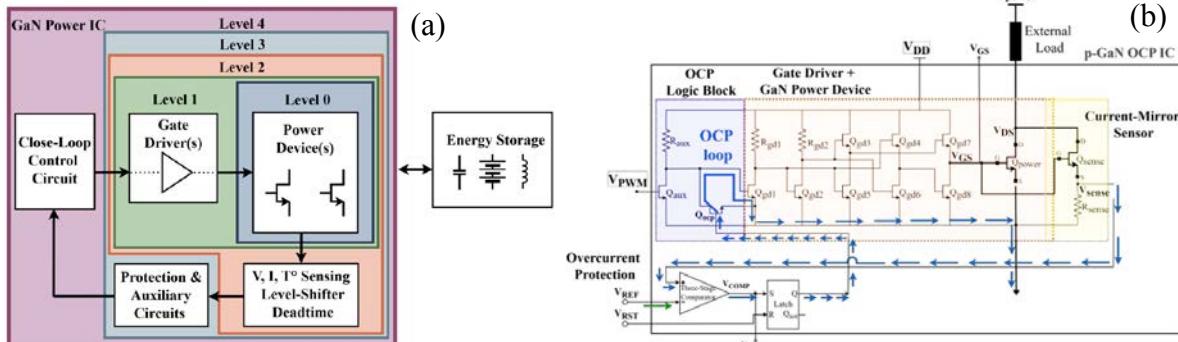

L'utilisation de circuit de gestion de puissance pour des récupérateur d'énergie nous a donné l'idée de généralisé ce concept à un système complet comprenant la boucle entre le dispositif de puissance au circuit de contrôle. Cette idée offre l'implémentation intégrale d'un système d'électronique de puissance qui peut exploiter toutes les performances de la technologie GaN et peut être utilisé pour des petites centrales de récupération d'énergie de type photovoltaïque. Rappelons que nous utilisons là encore la librairie de technologie p-GaN 200V développée par Imec qui ne propose que des HEMT à l'état normal OFF. Cela offre des performances plus équilibrées mais une logique complémentaire plus délicate à mettre en œuvre (11).

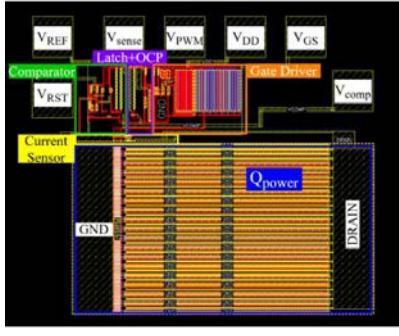

Le concept de System-on-Chip de puissance que nous mettons en œuvre dans ce projet, reprend celui du SoC faible puissance. Ce paradigme est alors appliqué à des technologies de haute puissance, on parle ici de 4kW géré par un circuit intégré sur 3mm<sup>2</sup>. Ce qui nous inspire dans cette démarche est le fait qu'en électronique de puissance existe 5 « niveaux d'intégration » (Fig. 5.a) chaque niveau assume une fonction électronique spécifique dans la chaîne de contrôle du dispositif de puissance. Un circuit en composants discrets, actifs et passifs limite les performances. On note entre autres les composantes parasites limitant la fréquence de fonctionnement, l'utilisation de bobines limitant la mise à l'échelle du circuit ou encore les problèmes de dissipation dans les résistances dû aux connexions. De plus ces circuits doivent être complétés par des systèmes auxiliaires utilisant une logique de détection de niveau. Ainsi, une solution complètement intégrée réduirait drastiquement ces effets négatifs et, en plus d'offrir des solutions dans les dimensions d'un microprocesseur, elle montrerait de très bonnes performances en fréquence. Dans cette perspective nous avons implémenté une solution complète de « SoC de puissance » qui comprend les 5 niveaux (Level 0 à Level 4) qui bien qu'à son niveau de développement initial, montre des performances très intéressante lors des simulations. Cette architecture que nous proposons intègre un interrupteur de puissance (Level 0), un gate driver (Level 1) (12), un détecteur à base de miroir de courant (Level 2) et un OCP basé sur un contrôle logique (Level 3) (13) et un circuit de control de boucle (Level 4). Non seulement il intègre les détecteurs mais il comprend en plus les systèmes auxiliaires de logique externe sur le même circuit intégré. La Fig. 5b montre le schéma hybride du SoC synoptique-électrique. Il indique la boucle fermée en cas d'excès de courant pour actionner la protection à titre d'exemple. Le Layout du SoC a été implanté en technologie p-GaN 200V sous Cadence Virtuoso (Fig. 6.a). Les simulations post layout montrent d'ores-et-déjà que ce système pourrait avoir un temps de réaction de 34ns, afin de limiter le courant à 12A et fonctionnerait à une fréquence 1MHz. Et rappelons qu'il pourrait supporter des puissances de l'ordre de 4kW pour une surface de GaN de 3mm<sup>2</sup>. Afin de vérifier ces performances plutôt exceptionnelles, le SoC a été fabriqué dans le cadre du programme ASCENT+ (Fig. 6.b). Le circuit suit une campagne de test en collaboration avec le laboratoire du GEEPS.

Fig.5. Architecture du System-on-Chip de puissance considérant tous les niveaux d'intégration d'un système en électronique de puissance adapté au concept de SoC. En (b) le schéma électrique propose le cas d'un excès de courant et la boucle de rétroaction pour protéger le dispositif de puissance avec une mise stand-by du circuit via le latch.

Fig.6. Le layout avec la description des connexions et des blocs fonctionnels de chaque niveau d'intégration du SoC en (a) et en (b) photographie du circuit intégré sous un microscope optique dans une station sous-pointe.

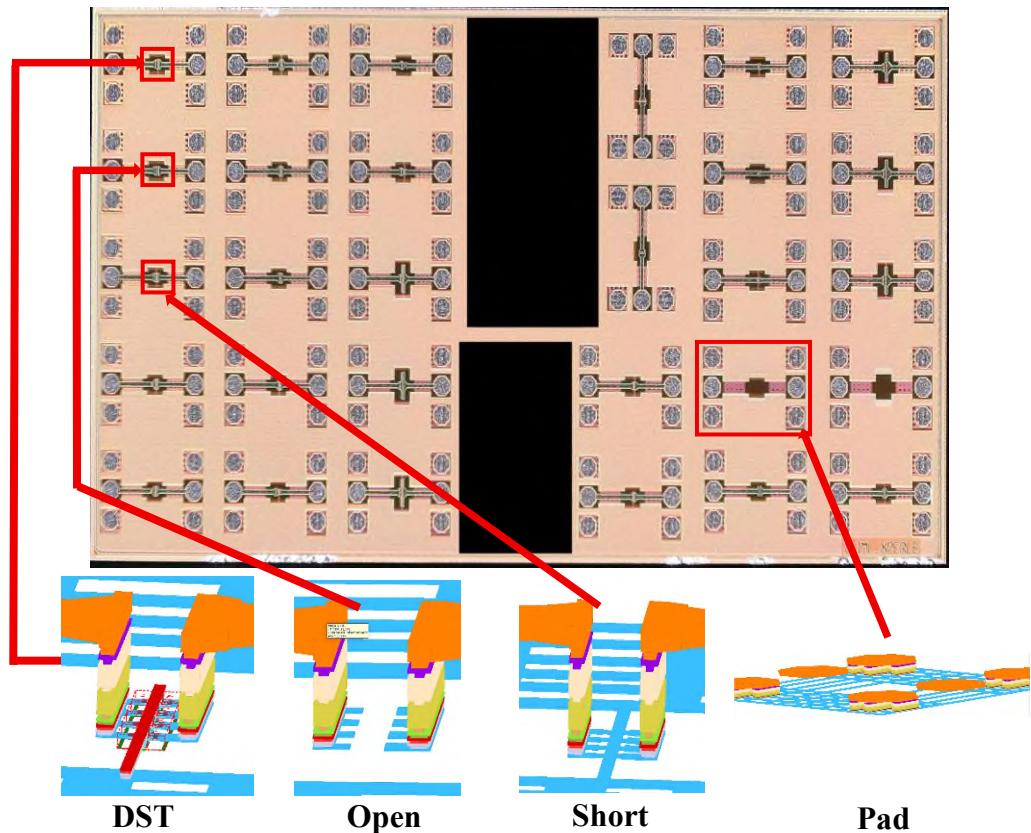

### III. L'empreinte digitale numérique : de l'ASIC 65nm à l'implémentation FPGA

La question de la sécurité des informations est soumise à une forme d'adaptation technologique qui surenchère de la complexité des systèmes. L'utilisation de fonctions mathématiques pour définir des protocoles en cryptographie en sont un exemple comme lorsque l'on passe du chiffre de César à Diffie-Hellman : le but reste le même mais les niveaux de complexité employé dans leur stratégie sont radicalement différents. Cependant les deux sont cassable si on y met les moyens de calcul suffisant et parfois si on trompe le système comme l'a montré Turing avec Enigma avec la cryptanalyse adéquate. Afin de dépasser ces limitations, un nouveau paradigme émerge en cryptographie qui se base sur les Physics Unclonable Functions (PUF). L'idée revient à exploiter la variabilité des process de fabrication responsable des variations en performance des dispositifs numériques et de l'associé à une empreinte digitale au sens humain du terme.

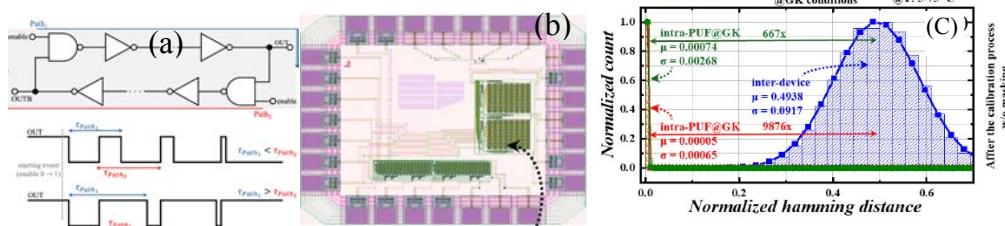

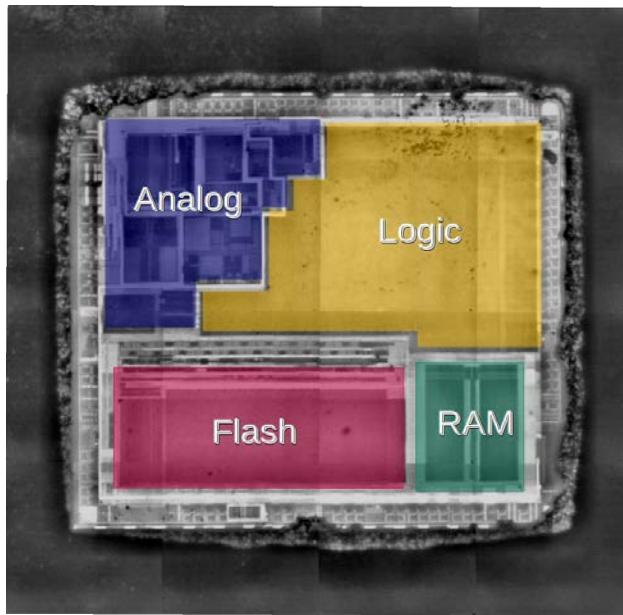

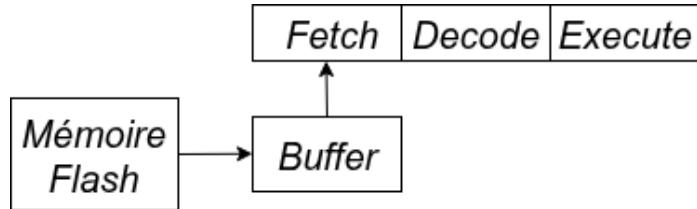

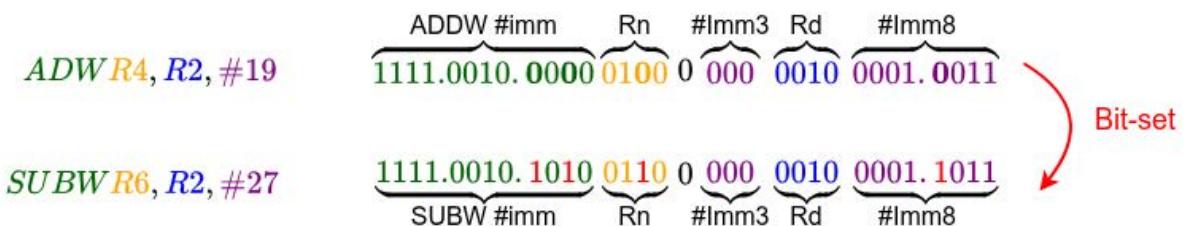

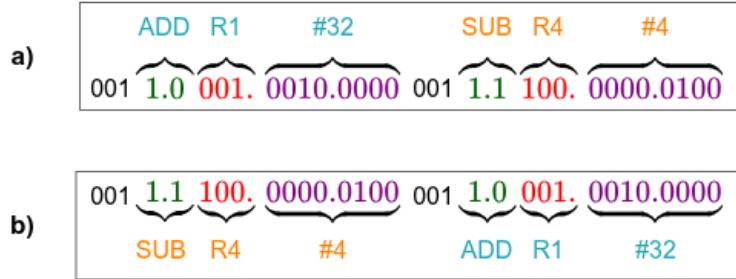

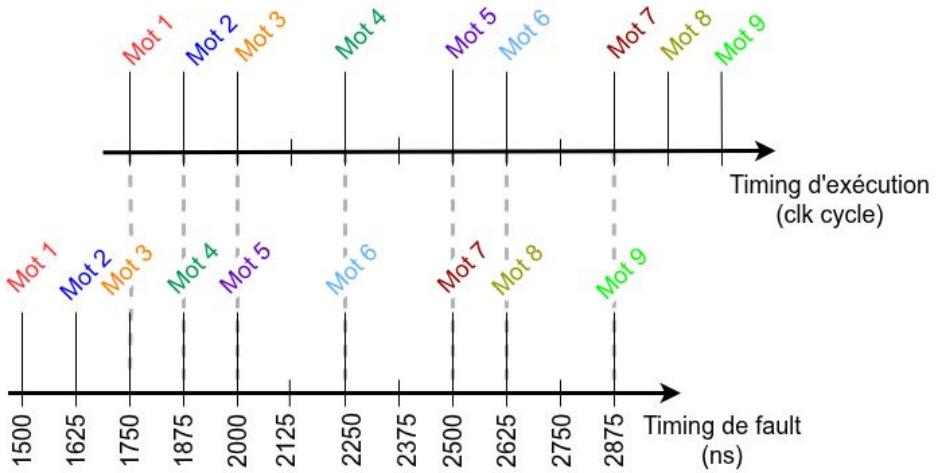

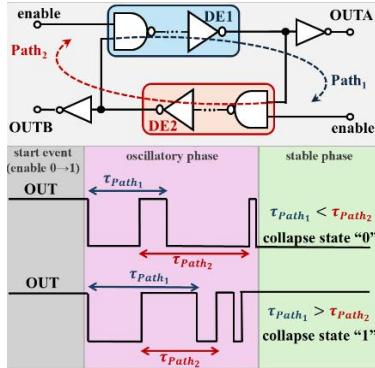

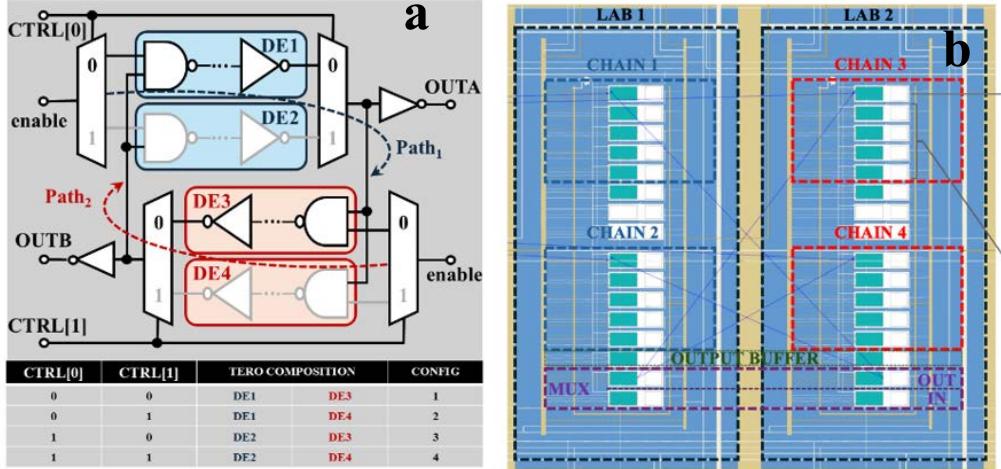

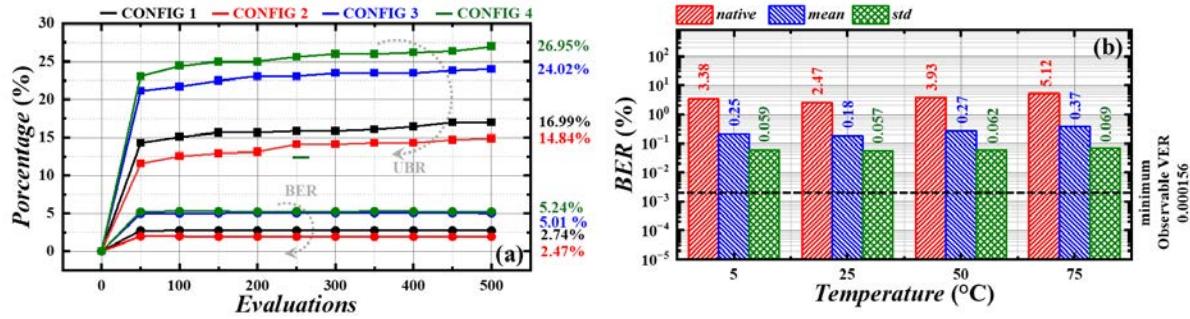

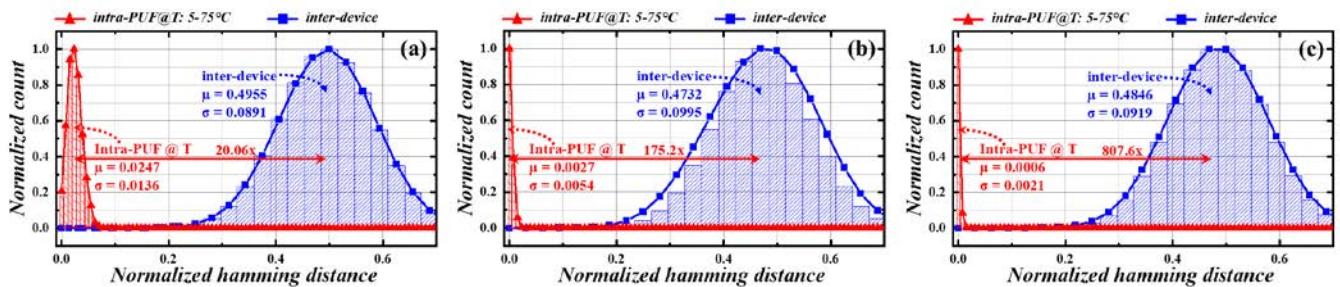

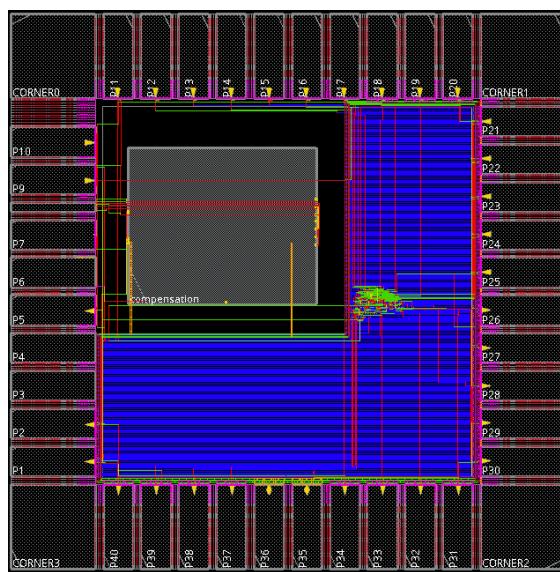

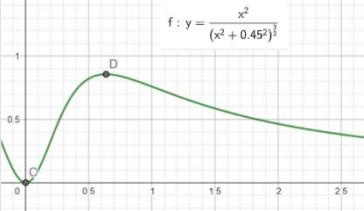

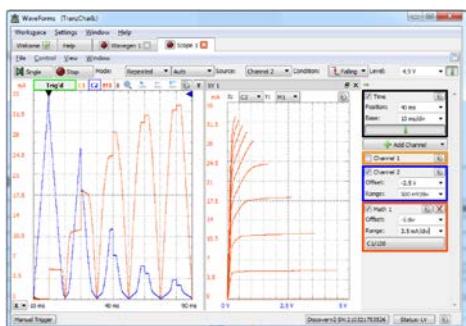

Dans ce travail (14) nous avons utilisé le principe de l'oscillateur en anneaux exploitant l'effet transitoire (TERO) explicité en Fig. 7.a. On comprend que suivant le chemin du signal l'oscillateur va collapser soit sur 1 soit 0 : ces délais sont des paramètres qui fluctuent en fonction de la variabilité du process de fabrication générant une réponse quasiment imprévisible. Nous avons développé le layout en 65nm (Fig. 7b) et les tests post layout montre une excellente unicité et reproductibilité avec le test de la distance de Hamming (Fig. 7c). L'utilisation d'une intégration ASIC offre plusieurs avantages comme BER natif proche de 0 et donc plus facile à calibrer, la rendant plus versatile : on peut configurer la PUF comme forte ou faible en plus d'une rapidité d'exécution. Le circuit a été fabriqué avec une technology TSMC dans le cadre du programme Europractice (Fig. 7.d) et en collaboration avec l'UNICAL (Italie).

Fig.7. En (a) le principe de fonctionnement du TERO lorsque les délais sont proches la PUF devient aléatoire et son entropie est maximisé. En (b) le layout fait en 65nm, la portion verte correspond au TERO designer. En (c) la distance de Hamming où la distance inter (gaussienne bleu) la valeur moyenne est proche de 0.5 avec une faible variance (bonne unicité) et la distance intra (gaussienne rouge) proche de 0 avec une séparation de près de 1000x après calibration (667x avant). En (d) le chip dans son packaging prêt pour les tests en laboratoire.

### I. Conclusion

Nous avons montré dans cette publication des travaux de recherche dans le LISITE à l'Isep conduit par des doctorants et des élèves de master. Ces travaux ont tous pu conduire à la fabrication d'un

circuit intégrés dans différentes technologies : 180nm, 65nm, et p-GaN. Bien que les circuits aient bien été reçus, ils sont pour la plupart en campagne de test et nous pourrons publier ces travaux dans des revues internationales de haut niveau à l'issus de ces tests. Cela contribue à consolider la méthodologie qui conduit aux étudiant.e.s master et docteurs de conclure leurs travaux de recherche par circuits afin de démontrer les résultats de leurs travaux de façon expérimentales. Mais plus important, les doctorants ont ainsi proposé des circuits complètement innovants comme un système de gestion de puissance haute tension en GaN pour des MEMS capacitif, un SoC de haute puissance (4kW sur 3mm<sup>2</sup>) et une PUF TERO avec des performances exceptionnelles et dont le concept est transposable sur des systèmes FPGA. Aussi il est essentiel de favoriser un environnement qui permet aux étudiant.e.s de fabriquer leur innovation par des collaborations entre l'académie et l'industrie de la micro et nanoélectronique.

### Remerciements

Les auteurs et spécifiquement les doctorants, souhaitent remercier le GIP et donc de la DGESIP, et le projet INFORISM (AMI-CMA) financé par l'ANR, convention N°ANR-23-CMAS-0024 pour l'accès au logiciel CADENCE. Nous souhaitons également remercier le programme ASCENT+ qui ont financé la fabrication des circuits GaN et l'Isep qui a financé leur diecing. Enfin nous souhaitons remercier le programme Europractice, l'IEEE R8 pour le soutien dans la fabrication des circuits AOP en 180nm et l'université de Bar-Ilan pour le packaging et l'université de Calabres pour le financement du circuit PUF en 65nm. Sans eux leur thèse et leurs travaux n'aurait jamais pu obtenir le niveau d'excellence atteint aujourd'hui.

### Références

1. Calvino, F., C. Criscuolo and A. Ughi (2024), "Digital adoption during COVID-19: Cross-country evidence from microdata", *OECD Science, Technology and Industry Working Papers*, No. 2024/03, OECD Publishing, Paris, <https://doi.org/10.1787/f63ca261-en>.

2. Trabelsi MA (2024), "The impact of artificial intelligence on economic development". *Journal of Electronic Business & Digital Economics*, Vol. 3 No. 2 pp. 142–155, doi: <https://doi.org/10.1108/JEBDE-10-2023-0022>

3. <https://www.theguardian.com/technology/2025/oct/29/nvidia-first-company-5-trillion>

4. [https://www.tsmc.com/english/dedicatedFoundry/technology/logic/l\\_A14](https://www.tsmc.com/english/dedicatedFoundry/technology/logic/l_A14)

5. <https://www.wired.com/story/the-rise-of-ai-is-forcing-google-and-microsoft-to-become-chipmakers/>

6. K. Vicuña *et al.*, "A 180 nm Low-Cost Operational Amplifier for IoT Applications," *2021 IEEE Fifth Ecuador Technical Chapters Meeting (ETCM)*, Cuenca, Ecuador, 2021, pp. 1-6, doi: 10.1109/ETCM53643.2021 (travail qui a remporté le prix de NEWCASS workshop student)

7. E. Holguin, « IP d'autonomie énergétique à base de MEMS capacitif en technologie GaN-on-Si », PhD manuscript archived at Sorbonne University, <https://theses.fr/2023SORUS672>.

8. E. Holguin, L. Trojman, L. M. Procel, A. Brenes and A. Vladimirescu, "Design and optimization of a Vibrational MEMS-Based Energy Harvester," *2022 17th Conference on Ph.D Research in Microelectronics and Electronics (PRIME)*, Villasimius, SU, Italy, 2022, pp. 209-212, doi: 10.1109/PRIME55000.2022.9816839. (pix du Meilleur papier étudiant)

9. E. Holguín, L. M. Prócel, A. Brenes, A. Vladimirescu and L. Trojman, "Analysis and Design of a Self-Powered VEH System Based on ULP Comparator," *2023 IEEE 14th Latin America Symposium on Circuits and Systems (LASCAS)*, Quito, Ecuador, 2023, pp. 1-4, doi: 10.1109/LASCAS56464.2023.10108276.

10. [https://www.imec-int.com/drupal/sites/default/files/2019-05/GAN%20ICS%20for%20integration%20of%20power%20systems\\_updated2019.pdf](https://www.imec-int.com/drupal/sites/default/files/2019-05/GAN%20ICS%20for%20integration%20of%20power%20systems_updated2019.pdf)

11. N. Pozo, L. -M. Prócel and L. Trojman, "Enhancement-mode p-GaN Comparators for power applications," *2023 18th Conference PRIME*, Valencia, Spain, 2023, pp. 197-200

12. N. Pozo, L. -M. Prócel and L. Trojman, "Design of a Gate Driver Based-on E-mode p-GaN HEMTs Handling 650V/10A GaN Power Device," *2024 22nd IEEE Interregional NEWCAS Conference (NEWCAS)*, Sherbrooke, QC, Canada, 2024, pp. 333-337, doi: 10.1109/NewCAS58973.2024.10666324.

13. N. Pozo, L. -M. Prócel and L. Trojman, "All-GaN Integrated Overcurrent Protection Circuit Using Only Enhancement-mode p-GaN Devices," *2024 37th SBC/SBMicro/IEEE Symposium on Integrated Circuits and Systems Design (SBCCI)*, Joao Pessoa, Brazil, 2024, pp. 1-5, doi: 10.1109/SBCCI62366.2024.10703983.

14. K. Vicuña, M. Vatalaro, F. Amiel, F. Crupi and L. Trojman, "Highly Stable Reconfigurable TERO PUF Architecture for Hardware Security Applications," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 33, no. 10, pp. 2873-2882, Oct. 2025, doi: 10.1109/TVLSI.2025.3587502.

# Une nouvelle approche de la stabilité des pérovskites pour une technologie photovoltaïque adaptée aux besoins énergétiques des objets numériques

L.A Egbunu-David<sup>a,b</sup>, N. Doumit<sup>a</sup>, E. Ntsoenzok<sup>b</sup>, L. Trojman<sup>a</sup>

<sup>a</sup> LISITE, Institut supérieur d'électronique de Paris (Isep), 92130 Issy-les-Moulineaux, France,

<sup>b</sup> CEHMTI, Centre national de la recherche scientifique (CNRS), 45071, Orléans, France.

E-mail de contact : [lilian.david-egbunu@ext.isep.fr](mailto:lilian.david-egbunu@ext.isep.fr)

## Abstract

L'évolution rapide des dispositifs connectés et numériques exige des matériaux semi-conducteurs qui combinent des performances optoélectroniques élevées avec une stabilité opérationnelle à long terme. Les pérovskites aux halogénures métalliques, en particulier l'iodure de plomb de formamidinium ( $\text{FAPbI}_3$ ), offrent des propriétés exceptionnelles d'absorption de la lumière et de transport des porteurs de charge, mais restent limitées par la métastabilité de leur  $\alpha$ -phase noire photoactive, qui se transforme facilement en  $\delta$ -phase jaune non photoactive à température ambiante. Dans cette étude, des calculs de la théorie de la fonctionnelle de la densité (DFT) ont été effectués pour comprendre les propriétés électroniques et optiques intrinsèques du  $\alpha$ - $\text{FAPbI}_3$  tridimensionnel (3D) et de son analogue bidimensionnel (2D)  $\text{BA}_2\text{FAPb}_2\text{I}_7$ . La phase 3D présente un gap direct de 1,48 eV et une forte absorption de la lumière visible, tandis que la phase 2D présente un gap plus large de 2,09 eV et un confinement électronique amélioré. L'analyse de la densité d'états projetée confirme l'existence d'une compatibilité électronique Pb-I partagé, assurant une interface entre ces matériaux. Ces résultats démontrent comment les couches de pérovskite 2D peuvent stabiliser la phase  $\alpha$  de  $\text{FAPbI}_3$ , offrant une voie prometteuse pour le développement de matériaux durables et performants pour les dispositifs microélectroniques, photoniques et de capteurs de nouvelle génération.

## I. Introduction

L'augmentation exponentielle des objets connectés et, plus généralement, de l'utilisation de l'énergie électronique dans le fonctionnement des technologies modernes(1) soulève une question cruciale : comment pouvons-nous soutenir l'alimentation électrique et la consommation d'énergie de ces appareils ? Une façon de répondre à cette question est sans aucun doute de redesigner les circuits pour les rendre moins énergivores tout en conservant des performances adéquates. Cependant, cela ne freine pas la production croissante d'appareils numériques. Depuis plusieurs décennies, les récupérateurs d'énergie proposent une solution pour réduire la dépendance à une source d'énergie électrique centralisée, dont plus de 60 % est obtenue à partir d'énergies fossiles(2). Leur intégration dans les systèmes électroniques (SoC) est assez bien acceptée dans les conceptions, mais leur efficacité reste une question difficile à maîtriser, nous ramenant souvent aux propriétés physiques des matériaux et aux phénomènes qui s'y produisent à l'échelle atomique. Pour prendre l'exemple de la technologie de récupération d'énergie la plus répandue dans les systèmes électroniques, le Photovoltaïque repose sur l'effet photoélectrique, où l'interaction électron-photon

dépend de la nature du matériau utilisé. Dans le cas du silicium, le matériau le plus mature de cette technologie, l'efficacité quantique, c'est-à-dire le rapport d'énergie électrique obtenu pour un photon absorbé par le matériau, est d'environ 25 %. On peut alors se demander s'il ne serait pas judicieux de remplacer le silicium par un autre matériau plus performant. La réponse, bien sûr, dépend : 1) de sa stabilité et de sa fiabilité, et 2) de sa compatibilité avec le silicium et les systèmes électroniques.

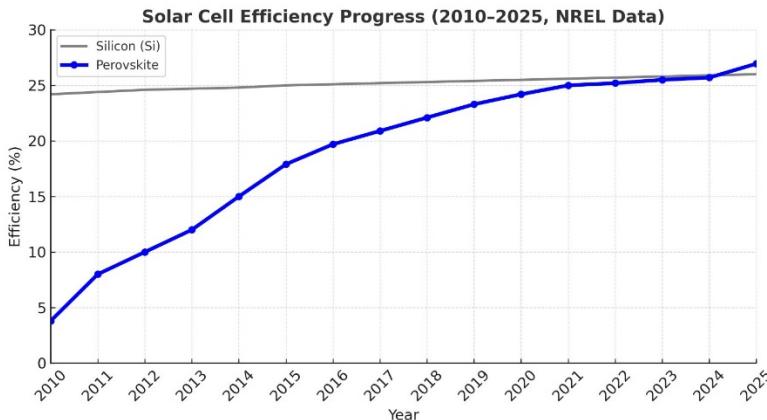

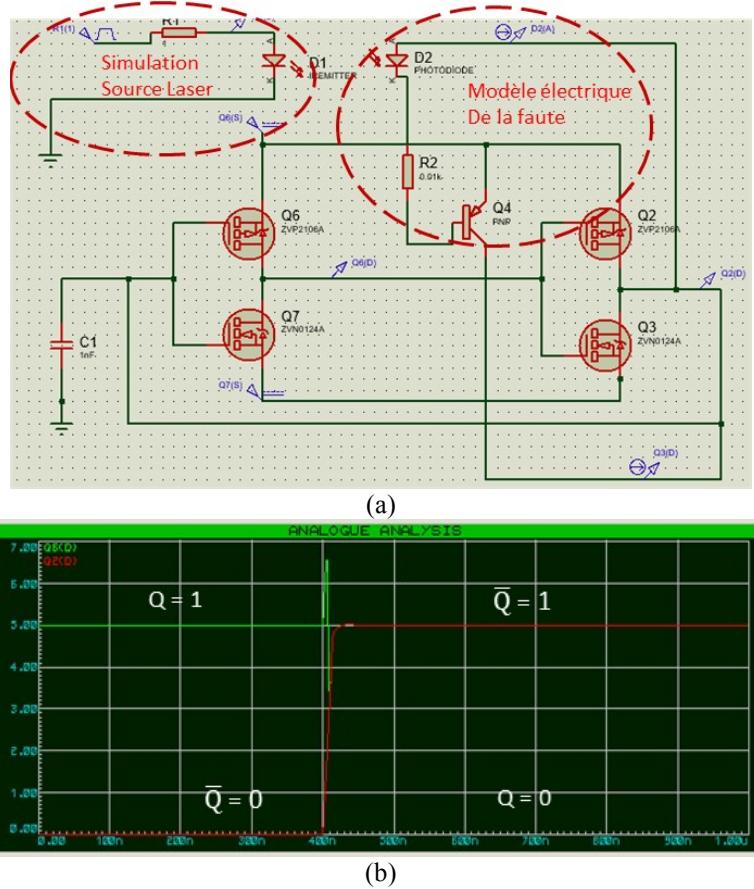

Fig. 1. Évolution technologique dans l'utilisation des matériaux semi-conducteurs, du silicium et des pérovskites. Les pérovskites ont suivi une tendance à la hausse, dépassant récemment la technologie du silicium(3).

Une revue de l'évolution de l'efficacité des matériaux photovoltaïques nous a amenés à nous intéresser aux matériaux pérovskites (Fig. 1). En effet, les dispositifs à pérovskite ont récemment montré une meilleure efficacité et un potentiel de croissance plus prononcé que ceux en silicium. Leurs performances exceptionnelles proviennent de leurs propriétés uniques : modulation du gap, coefficients d'absorption élevés, longues longueurs de diffusion des porteurs et mobilités élevées des porteurs de charge. Cependant, les matériaux à base de pérovskite présentent une faible fiabilité, ce qui s'explique par des problèmes de stabilité causés par l'humidité ambiante, entre autres (4).

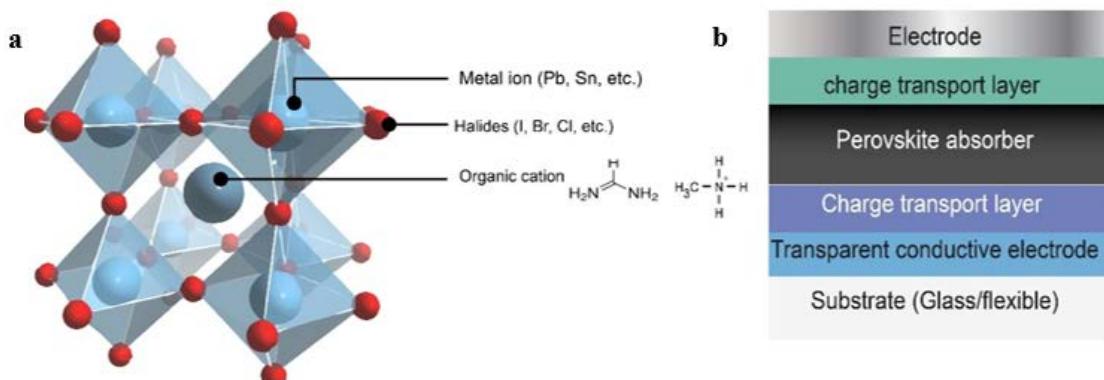

Il peut cependant y avoir un moyen de les rendre plus stables. Les pérovskites ont une structure de type substrat, donc avec une configuration atomique 3D similaire au silicium, à la différence que plusieurs types de matériaux sont impliqués dans la structure cristalline, notamment des métaux, des halogénures et des cations organiques (Fig. 2a). De plus, ils sont parfaitement adaptés pour une intégration dans une pile (« stack ») de dispositifs optoélectroniques pour des applications photovoltaïques (Fig. 2b).

Fig. 2. Un exemple de cellule pérovskite primitive avec l'architecture « gate stack » dans un dispositif photovoltaïque(5).

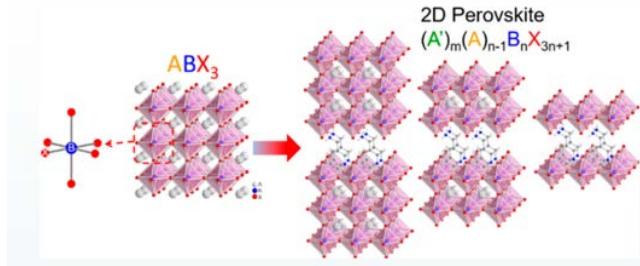

Pour compenser l'instabilité des pérovskites, l'idée est de les recouvrir d'une couche de matériau 2D ayant une base atomique similaire pour « les contenir » et rendre le système plus stable. En effet les pérovskites 2D ont une structure en couches avec des cations d'espacement organiques volumineux, ce qui leur confère une bonne stabilité(6). Dans notre cas, nous avons décidé de travailler avec des pérovskites de configuration cristalline  $ABX_3$ , et plus particulièrement avec de l'iodure de plomb de formamidinium ( $FAPbI_3$ ) et l'iodure de plomb de butylammonium et de formamidinium 2D  $BA_2^+ FAPb_2^- I_7^-$  (Fig. 3).

Fig. 3. Illustration schématique de la transformation structurelle de la pérovskite 3D  $ABX_3$  à la pérovskite 2D Ruddlesden-Popper en couches  $(A')_m(A)_{n-1}B_nX_{3n+1}$  (7)

Pour comprendre les interactions entre les substrats 3D et 2D et la faisabilité d'un dispositif à base de pérovskite, nous avons étudié les caractéristiques électriques de ces matériaux par le biais d'une analyse théorique pour comprendre leur structure électronique, leur densité d'états et leur diagramme de bande.

## II. Etude préliminaire à l'aide de la théorie de la fonctionnelle de la densité (DFT)

La DFT est une approche intéressante car elle permet une étude relativement précise de la structure électronique et permet de prédire les caractéristiques électroniques d'un matériau. La DFT intègre le concept de densité électronique, ce qui simplifie le problème complexe à N corps des électrons en interaction. La DFT réduit la complexité de calcul d'un problème à 3N dimensions (où N est le nombre d'électrons) à un problème à 3 dimensions en se concentrant sur la densité électronique plutôt que sur la fonction d'onde de chaque électron. Cette réduction améliore considérablement l'efficacité de calcul, ce qui permet d'étudier des systèmes atomiques plus grands(8). Les calculs DFT peuvent être utilisés pour mieux comprendre les effets de l'incorporation de la pérovskite 2D sur le gap, les masses effectives des porteurs de charge et les spectres d'absorption optique sur le  $FAPbI_3$ . La compréhension du mécanisme de stabilisation peut également être obtenue en clarifiant les interactions à l'interface  $BA_2FAPb_2I_7$  (2D) et  $FAPbI_3$  (3D).

Dans notre étude, nous avons choisi d'utiliser le logiciel Quantum ATK de la suite Synopsys. La stratégie consiste à utiliser les paramètres de structure électronique obtenus à partir de la DFT et à les intégrer dans un modèle physique pour la simulation au niveau du dispositif à l'aide de Sentaurus TCAD. Enfin, l'objectif est d'appliquer ce modèle physique à la simulation électrique avec CDesigner et de tester ses performances électriques dans un circuit dans des conditions quasi réelles. Les modifications du modèle physique peuvent ensuite être exportées pour diverses applications dans les circuits électriques afin d'évaluer la récupération d'énergie et son efficacité dans un contexte technologique donné.

## III. Résultats et discussion

Nous présentons ici l'analyse computationnelle des propriétés structurelles, électroniques et optiques des systèmes de pérovskites 3D  $FAPbI_3$  et 2D  $BA_2^+ FAPb_2^- I_7^-$ , et interprétons leurs

implications pour une cellule solaire à pérovskite stabilisée. Pour ces calculs nous avons utilisé la fonction d'échange-corrélation des électrons pour la pérovskite 2D à l'aide de la fonction d'approximation de gradient généralisée (GGA) développée par Perdew-Burke-Ernzerh (PBE). Le pseudopotentiel du pseudo Dojo et l'ensemble de base de la combinaison linéaire d'orbitales atomiques (LCAO) ont été utilisés et, une correction de dispersion D2 de Grimme a été incorporée pour tenir compte des interactions de Van der Waals. Nous avons utilisé la fonction hybride Heyd-Scuseria-Ernzerhof (HSE06) pour calculer les structures électroniques de la pérovskite 3D. Un milieu de base fixé par un pseudo potentiel de type Pseudo Dojo a été utilisé. L'échantillonnage de la zone Brillouin a utilisé une grille de points k Monkhorst-Pack ( $6 \times 6 \times 6$  pour la 3D,  $7 \times 7 \times 2$  pour la 2D), et une énergie de coupure de 300 eV. Les structures géométriques sont relaxées grâce à l'utilisation de l'optimiseur Broyden– Fletcher-Goldfarb-Shanno (LBFGS) à mémoire limitée.

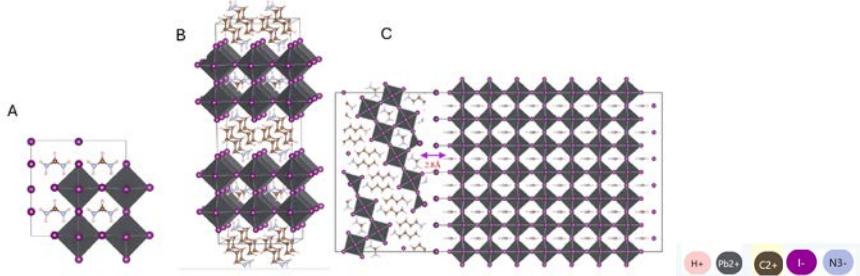

Fig. 4. Structures cristallines de, (A). 3D-FAPbI<sub>3</sub> (B) 2D-BA<sub>2</sub>FAPb<sub>2</sub>I<sub>7</sub> (C) Hétérostructure 3D/2D avec un vanderWaalsgap typique de 2,8 Å. Les octaèdres respectifs de PbI<sub>6</sub> sont marqués en gris, et les atomes sont marqués de Pb (gris), I (violet), C (marron), N (bleu) et H (rose). Les constantes du réseau de la structure 3D sont  $a=6.343\text{ \AA}$ ,  $b=6.343\text{ \AA}$ ,  $c=6.343\text{ \AA}$ ,  $\alpha=\beta=\gamma = 90^\circ$ , et celles de la structure 2D sont  $a=6.4884\text{ \AA}$ ,  $b=6.503\text{ \AA}$ ,  $c=19.0571\text{ \AA}$ ,  $\alpha=\beta=\gamma = 90^\circ$ .

Nous présentons d'abord la structure cristalline des pérovskites 2D, 3D et hybrides, et leur structure composite. Les structures prototypiques ont été obtenues à partir de calculs de structure électronique de type « first-principle » dans QuantumATK, comme le montre la Fig. 4.

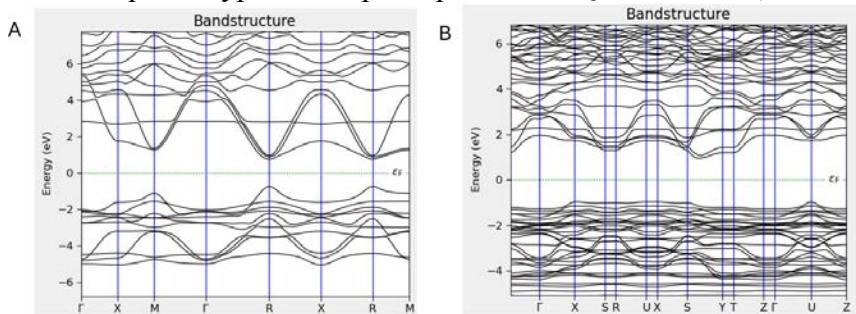

Fig. 5. Band Structure de (A) FAPbI<sub>3</sub> (B) BA<sub>2</sub> FAPb<sub>2</sub> I<sub>7</sub>

D'après la simulation sur QATK, la phase cubique FAPbI<sub>3</sub> présente un gap de 1,48 eV (Figure 5A) consistent avec des dispositifs à haut rendement(9-11). En revanche, la structure 2D BA<sub>2</sub> FAPb<sub>2</sub> I<sub>7</sub> à un gap plus grand de 2,09 eV (Fig. 5B). cette différence de gap est cohérente les effets diélectriques et confinement quantique dans les pérovskites stratifiées de Ruddlesden-Popper ; band gap  $\sim 2.0\text{-}2.3$  eV pour les compositions  $n = 2$  (spacieur/FA)(12)13). La structure de bandes électroniques montre une disparité de dispersion CB et VB relativement raide pour le FAPbI<sub>3</sub> 3D. En revanche le BA<sub>2</sub> FAPb<sub>2</sub> I<sub>7</sub> 2D montre des dispersions plus aplatis indiquant des masses effectives plus grandes et un confinement plus important, suggérant un rôle de couche stabilisatrice pour la FAPbI<sub>3</sub>. Nous retrouvons avec la DFT (QATK) un résultat conforme aux études théoriques précédentes sur les pérovskites où la dimensionnalité réduite augmente la masse effective et limite la mobilité des porteurs(14).

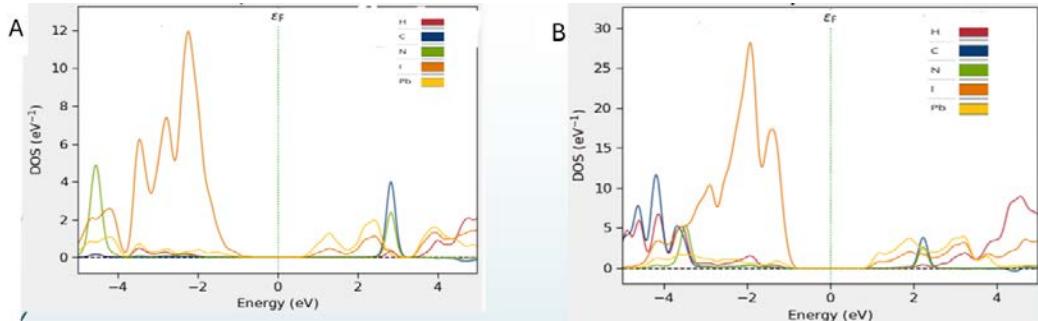

Fig. 6. Densité d'état projetée (PDOS) de (A)  $\text{FAPbI}_3$  (B)  $\text{BA}_2 \text{FAPb}_2 \text{I}_7$

Ces résultats sont confirmées la densité d'états projetée (PDOS) où le  $\text{FAPbI}_3$  (VB) montre une forte hybridation à travers la domination des états orbitaux p de l'iode (I-5P) sur le plomb (Pb-6s) alors que pour le  $\text{BA}_2 \text{FAPb}_2 \text{I}_7$  (VB) montre une faible hybridation des atomes organiques N et C qui réduit la mobilité pour un confinement plus important engendrant une meilleure stabilité structurelle contre l'humidité (13), (15). La CB est quant à elle dominé par des états 6p du plomb.

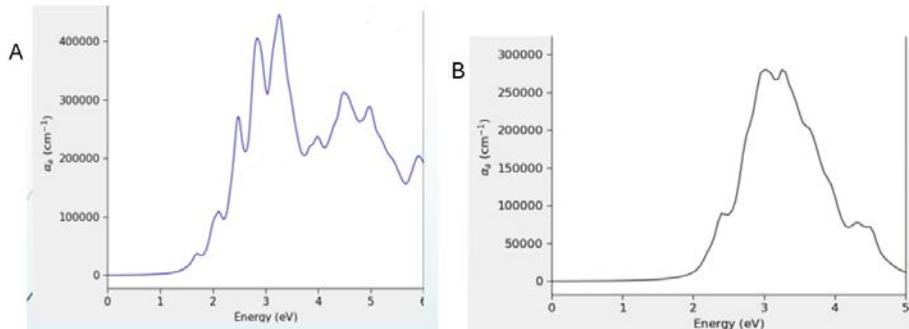

Fig. 7: Absorption optique de (A)  $\text{FAPbI}_3$  (B)  $\text{BA}_2 \text{FAPb}_2 \text{I}_7$  présente un coefficient d'absorption supérieur à  $4 \times 10^4 \text{ cm}^{-1}$  avec un début d'environ 1,5 eV, avec de multiples pics dans la gamme de 2 à 4 eV et une large absorption de la lumière visible.  $\text{BA}_2 \text{FAPb}_2 \text{I}_7$  a un coefficient plus faible ( $\sim 3 \times 10^4 \text{ cm}^{-1}$ ), un début à 2,0–2,1 eV et un spectre plus étroit.

Enfin l'absorption optique montre le décalage vers le bleu de la phase 2D, avec une absorption plus faible du rouge/proche infrarouge qui reflète ses effets sur le gap avec confinement plus larges. Cela soutient la stratégie d'utilisation de  $\text{BA}_2 \text{FAPb}_2 \text{I}_7$  comme couche stabilisatrice à large gap (absorbant moins de rouge/proche IR) tout en permettant à  $\text{FAPbI}_3$  d'agir comme l'absorbeur visible primaire(14)(16).

#### IV. Conclusion

Ce travail fournit une compréhension théorique détaillée des propriétés intrinsèques des pérovskites 3D  $\alpha\text{-FAPbI}_3$  et 2D  $\text{BA}_2 \text{FAPb}_2 \text{I}_7$ , des matériaux d'une importance croissante pour les dispositifs microélectroniques et optoélectroniques de nouvelle génération. Les résultats de la DFT révèlent que si  $\alpha\text{-FAPbI}_3$  possède un gap ou une bande interdite directe optimale et une forte absorption de la lumière visible (requises pour un fonctionnement photoélectrique actif), sa métastabilité structurelle dans les conditions ambiantes reste une limitation majeure. En revanche, la phase  $\text{BA}_2 \text{FAPb}_2 \text{I}_7$  en couches 2D, avec sa bande interdite plus large et son fort confinement électronique, offre une stabilité thermodynamique et environnementale supérieure.

Les travaux futurs étendront ces résultats pour inclure l'étude des propriétés électroniques de la pérovskite hybride 3D/2D, des effets interfaciaux et des effets de déformation afin de quantifier le rôle stabilisateur des couches supérieures 2D dans le maintien de la phase  $\alpha$  métastable de  $\text{FAPbI}_3$ . Il se concentrera également sur la validation expérimentale de l'hétérostructure 2D/3D par la fabrication de couches minces et des tests de stabilité de phase in situ dans des conditions ambiantes.

## V. Remerciements

Les auteurs souhaitent remercier le programme de Bourse PTDF pour le financement de la doctorante et le projet INFORISM (AMI-CMA) financé par l'ANR, convention N°ANR-23-CMAS-0024 pour l'accès au logiciel Quantum ATK de Synopsys.

## Références

1. S. Sinha, « Le nombre d'appareils IoT connectés augmente de 14 % pour atteindre 21,1 milliards ». Consulté le 10 novembre 2025. [En ligne]. Disponible : <https://iot-analytics.com/number-connected-iot-devices/>

2. J. L. Holechek, H. M. E. Geli, M. N. Sawalhah et R. Valdez, « Une évaluation mondiale : les énergies renouvelables peuvent-elles remplacer les combustibles fossiles d'ici 2050 ? », *Soutenir*. 2022, vol. 14, page 4792, vol. 14, n° 8, p. 4792, avr. 2022, doi : 10.3390/SU14084792.

3. « Graphique de la meilleure efficacité des cellules de recherche | Recherche photovoltaïque | NREL. Consulté le 10 novembre 2025. [En ligne]. Disponible : <https://www.nrel.gov/pv/cell-efficiency.html>

4. Y. Jiang, X. Wang et A. Pan, « Propriétés des excitons et des porteurs de charge photogénérés dans les pérovskites aux halogénures métalliques », *Adv. Mater.*, vol. 31, n° 47, p. 1806671, nov. 2019, doi : 10.1002/ADMA.201806671.

5. « Cellules solaires à pérovskite - Photovoltaïque imprimable. » Consulté le 10 novembre 2025. [En ligne]. Disponible : <https://research.csiro.au/printedpv/perovskite/>

6. G. Wu, R. Liang, M. Ge, G. Sun, Y. Zhang et G. Xing, « Passivation de surface à l'aide de pérovskites 2D vers des cellules solaires à pérovskites efficaces et stables », *Adv. Mater.*, vol. 34, n° 8, p. 2105635, févr. 2022, doi : 10.1002/ADMA.202105635.

7. L. Mao, C. C. Stoumpos et M. G. Kanatzidis, « Pérovskites hybrides bidimensionnelles aux halogénures : principes et promesses », *J. Am. Chem. Soc.*, vol. 141, n° 3, p. 1171-1190, janv. 2018, doi : 10.1021/JACS.8B10851.

8. J.-L. Bretonnet et J.-L. Bretonnet, « Bases de la théorie de la fonctionnelle de la densité », *AIMS Mater. Sci.* 2017 61372, vol. 4, no. 6, pp. 1372–1405, 2017, doi: 10.3934/MATERSCI.2017.6.1372.

9. M. T. Weller, O. J. Weber, J. M. Frost et A. Walsh, « Structure cubique de pérovskite de l'iodure de plomb de formamidinium noir,  $\alpha$ -[HC(NH<sub>2</sub>)<sub>2</sub>]PbI<sub>3</sub>, à 298 K », *J. Phys. Chem. Lett.*, vol. 6, no. 16, pp. 3209–3212, Aug. 2015, doi: 10.1021/ACS.JPCLETT.5B01432/SUPPL\_FILE/JZ5B01432\_SI\_002.MP4.

10. H. Moatassim, H. Zaari, A. El Kenz, A. Benyoussef, M. Loulidi et O. Mounkachi, « Étude théorique de l'efficacité de FAPbSnGeX<sub>3</sub> », *RSC Adv.*, vol. 12, n° 15, p. 8945-8952, mars 2022, doi : 10.1039/D2RA00345G.

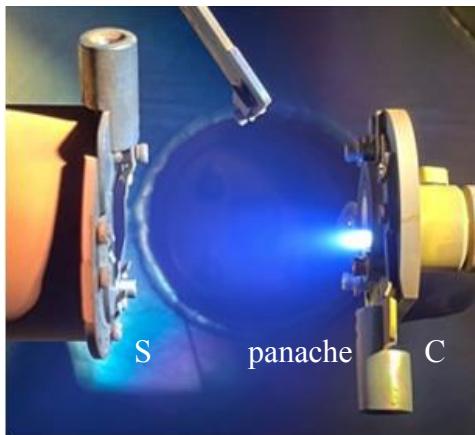

11. H. Min *et al.*, « Cellules solaires efficaces et stables en utilisant la bande interdite inhérente à l'iodure de plomb de formamidinium en phase  $\alpha$  », *Sciences (80-.)*, vol. 366, no. 6466, pp. 749–753, Nov. 2019, doi: 10.1126/SCIENCE.AAY7044.